#### University of South Carolina

### **Scholar Commons**

Theses and Dissertations

6-30-2016

## Finite Control Set Model Predictive Control Of Direct Matrix **Converter And Dual-Output Power Converters**

Ozan Gulbudak University of South Carolina

Follow this and additional works at: https://scholarcommons.sc.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Gulbudak, O.(2016). Finite Control Set Model Predictive Control Of Direct Matrix Converter And Dual-Output Power Converters. (Doctoral dissertation). Retrieved from https://scholarcommons.sc.edu/etd/ 3467

This Open Access Dissertation is brought to you by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact digres@mailbox.sc.edu.

## FINITE CONTROL SET MODEL PREDICTIVE CONTROL OF DIRECT MATRIX CONVERTER AND DUAL-OUTPUT POWER CONVERTERS

By

Ozan Gulbudak

Bachelor of Science Mersin University, 2008

Master of Science Mersin University, 2010

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

**Electrical Engineering**

College of Engineering and Computing

University of South Carolina

2016

Accepted by:

Enrico Santi, Major Professor

Herbert Ginn, Committee Member

Bin Zhang, Committee Member

Joshua Tarbutton, Committee Member

Lacy Ford, Senior Vice Provost and Dean of Graduate Studies

© Copyright by Ozan Gulbudak, 2016

All Rights Reserved.

#### **ACKNOWLEDGEMENTS**

The first person that I show my gratitude is Dr. Enrico Santi for his extensive support, guidance throughout my doctoral study here in USC. He has taught me much about research in power electronics and offered me such exciting research topic. It was priceless opportunity to work with Dr. Santi and in one of the most leading research group.

I would also like to express my gratitude to my committee members, Dr. Ginn, Dr. Zhang and Dr. Tarbutton for their feedback and helping me to improve my dissertation.

I am particularly indebted to Janosch Marquart from University of Applied Science NTB, Switzerland for helping to build several hardware platforms and it was great chance to work with him. I would also like to thank my colleagues, past and present, in Power Energy Group: Dr. Isaac Nam, Dr. Kang Peng, Dr. Hossein A. Mohammadpour, Dr. Alexander Grekov, Jonathan Siegers, Silvia Arrua, Soheila Eskandari, Vinya Sri Penchala, Hessamaldin Abdollahi, Hossein Baninajar.

#### **ABSTRACT**

Model Predictive Control (MPC) with a finite control set has been successfully applied to several power converter topologies as reported in the scientific literature and research activity on predictive control techniques has increased over the last few years. MPC uses a discrete-time model of the system to predict future values of control variables for all possible control actions and computes a cost function related to control objectives to find the optimal control action. The control action which minimizes the cost function is selected and applied to the system for the next time interval. Different control objectives can be introduced in the user-defined cost function and controlled simultaneously by solving the multi-objective optimization problem. This approach is particularly advantageous for certain power converter topologies, such as Direct Matrix Converter (DMC) and dual-output power converters, for which conventional control techniques require complicated Pulse Width Modulation (PWM) schemes and multi-loop control, incurring high computational burden and complexity. Conversely, since MPC does not need a modulator to generate switching signals, implementation of the MPC technique is simple and intuitive. However, the MPC method also has several drawbacks:

- 1. Real-time implementation of MPC incurs high computational burden

- 2. There is no analytical procedure to adjust the weighting factors for multiobjective optimization problem

- A complete system model must be derived since MPC method uses this model to predict control variables

- 4. MPC implementation is not straightforward for several power converter topologies, such as dual-output power converters.

In this dissertation four specific contributions are reported that address these drawbacks.

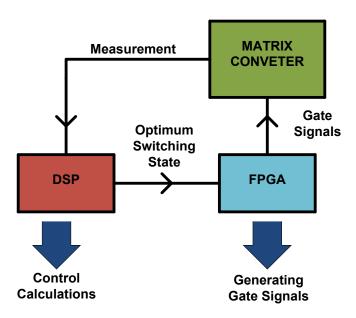

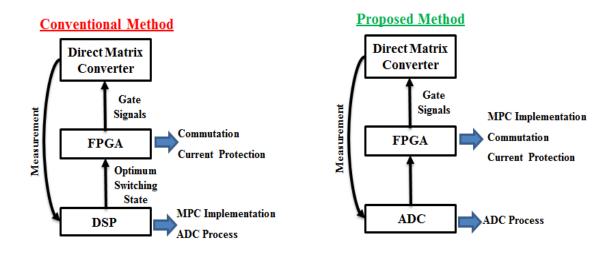

First, a fully FPGA-based real-time implementation of model predictive controller is proposed for direct matrix converter. In conventional real-time implementation of model predictive control method, Digital Signal Processors (DSPs) and Field-Programmable Gate Arrays (FPGA) are both used to ensure fast processing operation and preserve performance of the predictive controller. For the proposed, real-time implementation method, all control calculations and the safe commutation scheme for DMC are fully implemented in the FPGA and the need for a DSP is eliminated. Advantages of the proposed approach are simplicity and the ability to exploit the parallel computation capability of the FPGA to calculate in parallel the predictive state for all switch combination. This translates in a significant reduction of required computation time and potentially in reduced control hardware cost.

Second, a novel model predictive control scheme for the three-phase direct matrix converter based on switching state elimination is proposed. The conventional MPC solves a multi-objective optimization problem by minimizing a multi-objective cost function over a one-step horizon. The control performance is strongly affected by the weighting factors used in the cost function and this is problematic. The proposed method solves this difficulty by eliminating the weighting factors and using a state elimination method based on error constraints that have a clear physical interpretation.

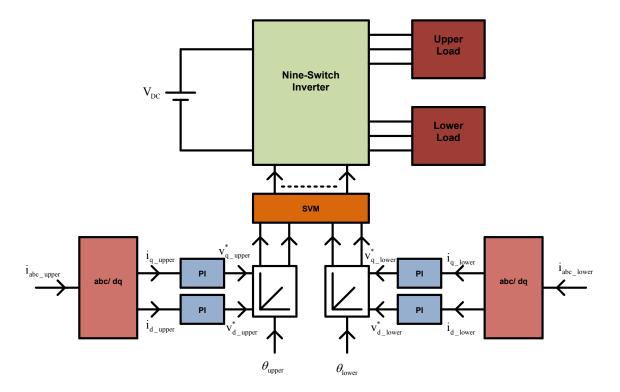

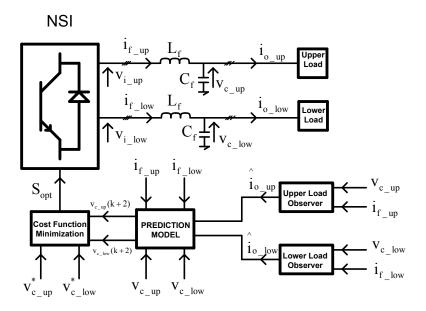

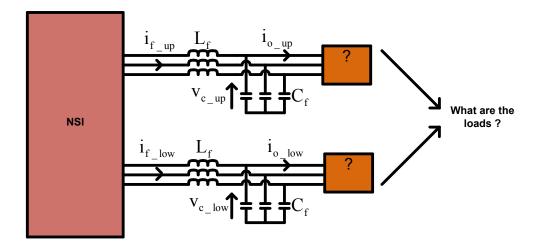

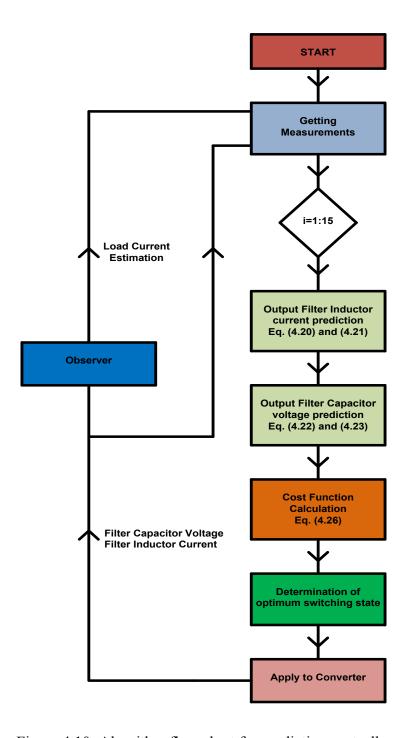

Third, the model predictive control scheme is proposed for Nine-Switch Inverter (NSI) under an unknown load condition. Nine-switch inverter is a dual-output inverter and the proposed method can control two three-phase load simultaneously by solving single optimization problem. In power electronics applications, control of the power converter must work well under all load conditions and the control method should provide clean power no matter what the load is. In this work, two ac load currents are estimated using full-order observers and converter is controlled by using model predictive control method.

Fourth, the model predictive control scheme is proposed for dual-output Indirect Matrix Converter (IMC). Modulation method for this topology is complicated and conventional linear control techniques require tuning of the controller parameters. In conventional control technique, multi-loop control is required to independently adjust the two ac outputs. The usage of multi-loop control techniques increases the complexity of implementation of the controller. On the other hand, proposed method can achieve several control goals by using single control loop and provide good system performance.

## TABLE OF CONTENTS

| ACKNO   | WLEDGEMENTS                                                       | iii |

|---------|-------------------------------------------------------------------|-----|

| ABSTRA  | ACT                                                               | iv  |

| LIST OF | TABLES                                                            | ix  |

| LIST OF | F FIGURES                                                         | x   |

| LIST OF | F SYMBOLS                                                         | xvi |

| СНАРТІ  | ER 1 INTRODUCTION                                                 | 1   |

| 1.1     | FINITE CONTROL SET MODEL PREDICTIVE CONTROL                       | 1   |

| 1.2     | DIRECT MATRIX CONVERTER                                           | 4   |

| 1.3     | DUAL OUTPUT NINE-SWITCH INVERTER                                  | 6   |

| 1.4     | DUAL-OUTPUT INDIRECT MATRIX CONVERTER                             | 8   |

| 1.5     | RESEARCH OBJECTIVES                                               | 9   |

|         | ER 2 FPGA-BASED MODEL PREDICTIVE CONTROLLER FOR DIF               |     |

| 2.1     | MATRIX CONVERTER                                                  |     |

| 2.1     | MODEL PREDICTIVE CONTROL FOR DIRECT MATRIX CONVERTER              |     |

| 2.2     | ISSUES WITH CONVENTIONAL REAL-TIME IMPLEMENTATION                 |     |

| 2.3     | PROPOSED REAL-TIME IMPLEMENTATION METHOD                          |     |

|         |                                                                   |     |

| 2.5     | HARDWARE PLATFORMS AND EXPERIMENTAL RESULTS                       |     |

| 2.6     | DISCUSSION AND CONCLUSION.                                        |     |

|         | ER 3 MODEL PREDICTIVE CONTROL BASED ON SWITCHING ST<br>LIMINATION |     |

| 3.1     | CONVENTIONAL MODEL PREDICTIVE CONTROL                             |     |

| 3.2     | SWITCHING STATE ELIMINATION TECHNIQUE                             | 44  |

| 3.3     | SIMULATION RESULTS                                                |     |

| 3.4     | Experimental Results                                              |     |

| 3.5     | Conclusion                                                        |     |

| CHAPT | ER 4 MODEL PREDICTIVE CONTROL FOR NINE-SWITCH INV                 | 'ERTER 64 |

|-------|-------------------------------------------------------------------|-----------|

| 4.1   | CONVENTIONAL CONTROL TECHNIQUE FOR NINE-SWITCH INVER              | ГЕR65     |

| 4.2   | System Model                                                      | 66        |

| 4.3   | MODEL PREDICTIVE CONTROL SCHEME                                   | 74        |

| 4.4   | SIMULATION RESULTS                                                | 78        |

| 4.5   | Summary                                                           | 90        |

|       | ER 5 MODEL PREDICTIVE CONTROL FOR DUAL-OUTPUT IN MATRIX CONVERTER |           |

| 5.1   | Introduction                                                      | 92        |

| 5.2   | System Model                                                      | 93        |

| 5.3   | MODEL PREDICTIVE CONTROL SCHEME                                   | 95        |

| 5.4   | SIMULATION RESULTS                                                | 97        |

| 5.5   | SUMMARY                                                           | 105       |

| CHAPT | ER 6 CONCLUSIONS AND FUTURE WORK                                  | 106       |

| 6.1   | Conclusions                                                       | 106       |

| 6.2   | Future Work                                                       | 108       |

| REFER | ENCES                                                             | 109       |

## LIST OF TABLES

| Table 1.1 Switches positions of Legs                                        | 8  |

|-----------------------------------------------------------------------------|----|

| Table 2.1 Switches positions of Legs                                        | 36 |

| Table 2.2 FPGA resources and execution time vs number of control objectives | 37 |

| Table 2.3 Digital control platforms comparison                              | 39 |

| Table 2.4 Execution time for calculation tasks                              | 40 |

| Table 3.1 Sub-finite solution set selection                                 | 47 |

| Table 3.2 Simulation parameters for first case                              | 51 |

| Table 4.1 Simulation Parameters                                             | 78 |

| Table 5.1 Simulation Parameters                                             | 98 |

## LIST OF FIGURES

| Figure 1.1 Working principle of model predictive control                                                   | 3        |

|------------------------------------------------------------------------------------------------------------|----------|

| Figure 1.2 General predictive control scheme for power converters                                          | 4        |

| Figure 1.3 Direct matrix converter topology                                                                | 5        |

| Figure 1.4 Switching combinations for direct matrix converter                                              | 6        |

| Figure 1.5 Nine-switch inverter topology                                                                   | 7        |

| Figure 1.6 Dual-Output Indirect Matrix Converter Topology                                                  | 9        |

| Figure 2.1 Model predictive control scheme for direct matrix converter                                     | 19       |

| Figure 2.2 Conventional real-time implementation for direct matrix converter                               | 21       |

| Figure 2.3 Comparison between conventional method and proposed method                                      | 22       |

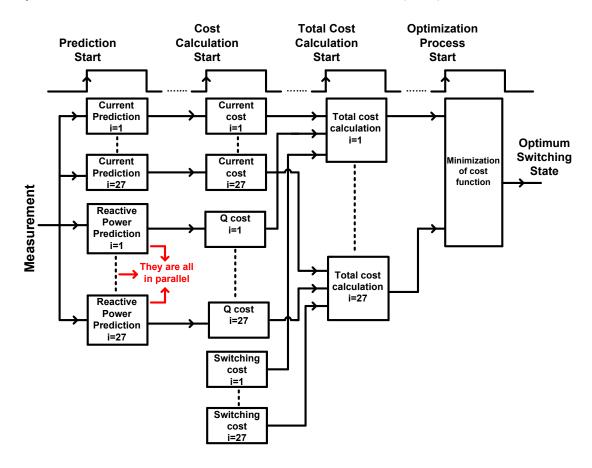

| Figure 2.4 Parallel implementation of model predictive control.                                            | 23       |

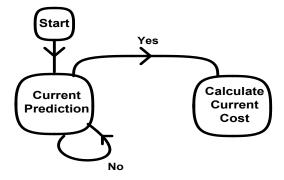

| Figure 2.5 Finite state machine for current cost calculation.                                              | 23       |

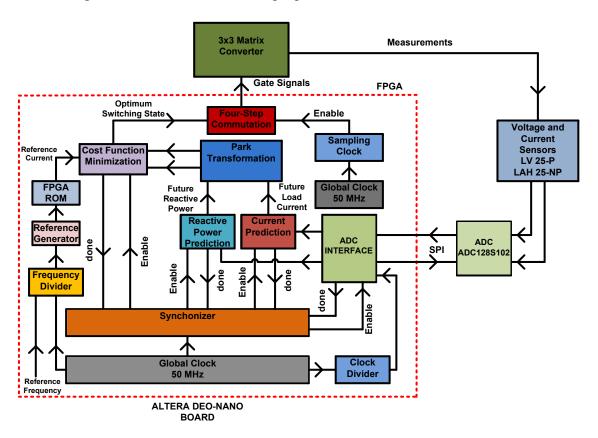

| Figure 2.6 FPGA architecture for predictive controller.                                                    | 24       |

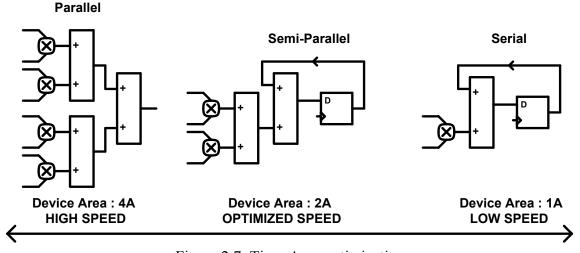

| Figure 2.7 Time-Area optimization.                                                                         | 25       |

| Figure 2.8 Two-phase input single-phase output topology                                                    | 26       |

| Figure 2.9 Two-phase input single-phase output prototype                                                   | 27       |

| Figure 2.10 Output load current measurement circuit.                                                       | 28       |

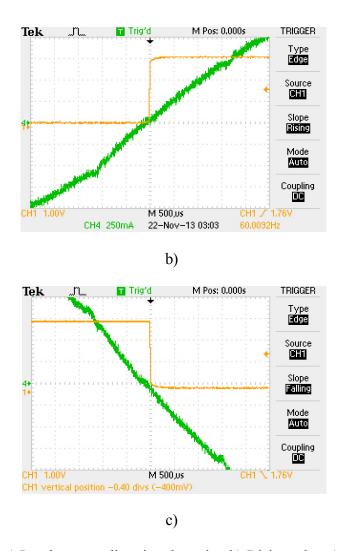

| Figure 2.11 Load current direction sensing wavefom a)Load current direction b) Rising edge c) Falling edge |          |

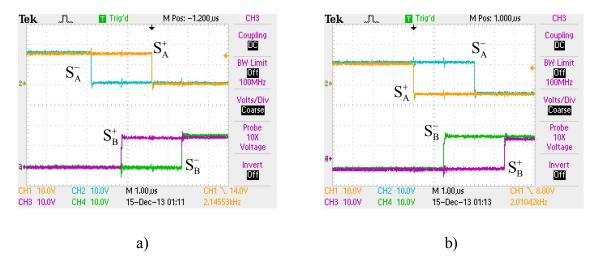

| Figure 2.12 Four-step commutation a) Positive load current b) Negative load c                              | urrent30 |

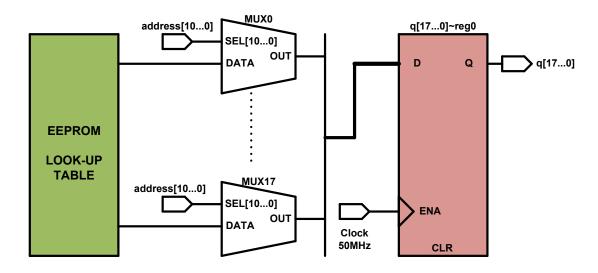

| Figure 2.13 RTL for reference generation.                                                                                                                                 | 31 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.14 Reference generation using ROM block.                                                                                                                         | 31 |

| Figure 2.15 Direct matrix converter prototype.                                                                                                                            | 32 |

| Figure 2.16 Experimental results in case of 60 Hz reference a) Experimental wavefor without reactive power control b) Experimental waveforms with reactive power control. | er |

| Figure 2.17 Experimental results in case of 30 Hz reference a)Experimental waveform b) Load current frequency spectrum c) Source current frequency spectrum               |    |

| Figure 2.18 Experimental results in case of 120 Hz reference a) Experimental waveforms b) Load current frequency spectrum c) Source current frequency spectrum            |    |

| Figure 2.19 Dynamic response of FPGA-based model predictive controller                                                                                                    | 36 |

| Figure 2.20 Calculation loop comparison a) MPC implementation by using serial-computing device b) MPC implementation by fully paralleling technique                       | 38 |

| Figure 3.1 Conventional model predictive control scheme for first case                                                                                                    | 43 |

| Figure 3.2 Conventional model predictive control scheme for second case.                                                                                                  | 44 |

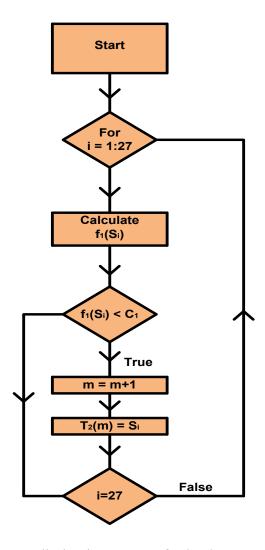

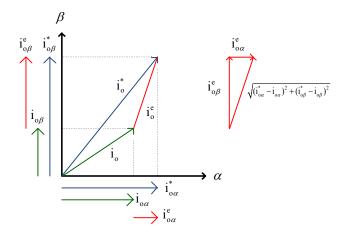

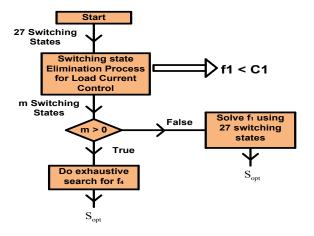

| Figure 3.3 Switching state elimination process.                                                                                                                           | 46 |

| Figure 3.4 Elimination process for load current control.                                                                                                                  | 47 |

| Figure 3.5 Vector representation of current error term.                                                                                                                   | 49 |

| Figure 3.6 Algorithm flow chart for proposed method for second case                                                                                                       | 50 |

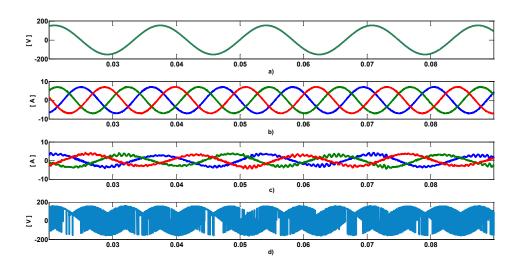

| Figure 3.7 Simulation results for CASE 1 (45 Hz load current reference) a) Supply voltage b) Load current c) Supply current d) Output load voltage                        | 51 |

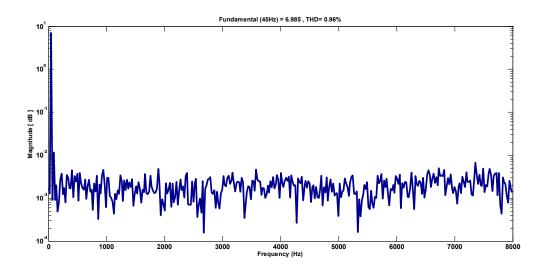

| Figure 3.8 Frequency spectrum of load current (Case 1 and 45 Hz load current reference)                                                                                   | 52 |

| Figure 3.9 Frequency spectrum of source current (Case 1 and 45 Hz load current reference)                                                                                 | 52 |

| Figure 3.10 Simulation reults for CASE 1 (90 Hz load current reference) a) Supply voltage b) Load current c) Supply currentd) Output load voltage                         | 53 |

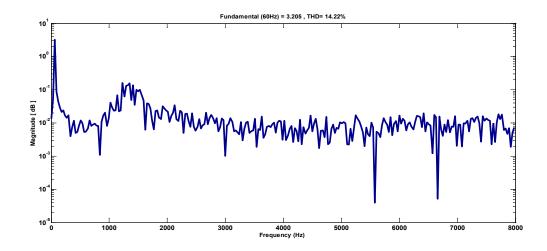

| Figure 3.11 Frequency spectrum of load current (Case 1 and 90 Hz load current reference)                                                                                  | 53 |

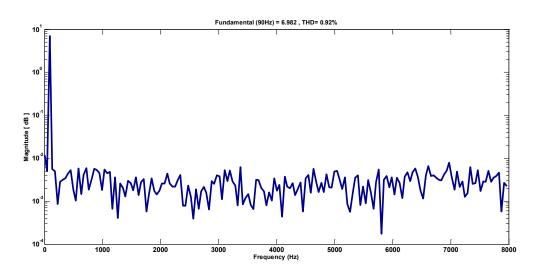

| Figure | Figure 3.12 Frequency spectrum of load current (Case 1 and 90 Hz load current reference)                                                 |    |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Figure | reference)                                                                                                                               |    |  |  |

| Figure | 3.14 Phase plane plot of load current .                                                                                                  | 55 |  |  |

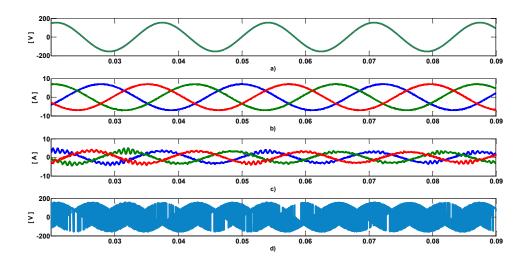

| Figure | 3.15 Simulation results for Case 2 (50 Hz load current) a) Supply voltage b) Loa current c) Supply current d) Output load voltage        |    |  |  |

| Figure | 3.16 Frequency spectrum of load current (Case 2 and 50 Hz load current reference)                                                        | 56 |  |  |

| Figure | 3.17 Frequency spectrum of source current (case 2 and 50Hz load current reference)                                                       | 56 |  |  |

| Figure | 3.18 Experiemental results in case of 45 Hz load current frequency                                                                       | 57 |  |  |

| Figure | 3.19 FFT analysis of load current (45 Hz load current reference) a) Load current measurement b) Frequency spectrum of load current       |    |  |  |

| Figure | 3.20 FFT analysis of source current (45 Hz load current reference) a) Source current measurement b) Frequency spectrum of source current | 58 |  |  |

| Figure | 3.21 Experimental result in case of 60 Hz load current frequency                                                                         | 59 |  |  |

| Figure | 3.22 FFT analysis of load current (60 Hz load current reference) a) Load current measurement b) Frequency spectrum of source current     |    |  |  |

| Figure | 3.23 FFT analysis of source current (60 Hz load current reference) a) Source current measurement b) Frequency spectrum of source current | 60 |  |  |

| Figure | 3.24 Experimental result in case of 90 Hz load current frequency                                                                         | 60 |  |  |

| Figure | 3.25 FFT analysis of load current (90 Hz load current reference) a) Load current measurement b) Frequency spectrum of source current     |    |  |  |

| Figure | 3.26 FFT analysis of source current (90 Hz load current reference) a) Source current measurement b) Frequency spectrum of source current | 61 |  |  |

| Figure | 4.1 Conventional control method for nine-switch inverter                                                                                 | 65 |  |  |

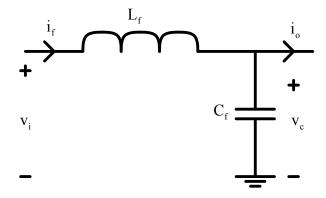

| Figure | 4.2 Nine-switch inverter with output filter                                                                                              | 67 |  |  |

| Figure | 4.3 Output filter model.                                                                                                                 | 68 |  |  |

| Figure | 4.4 Output LC filter model .                                                                                                             | 68 |  |  |

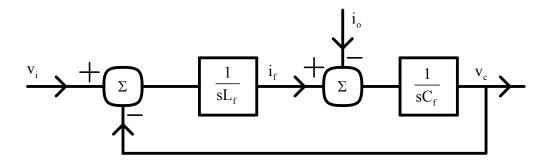

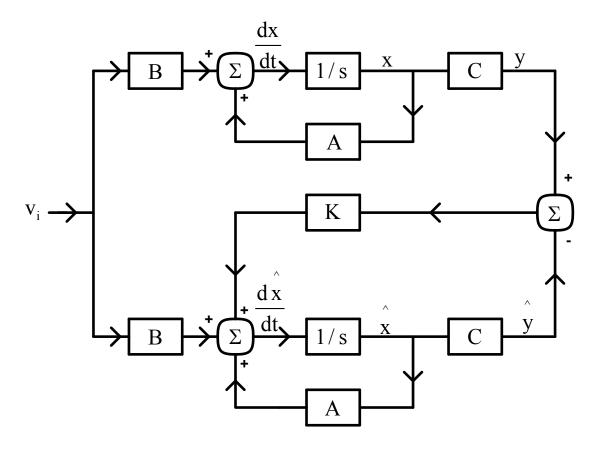

| Figure | 4.5 Block diagram of the system and observer.                                                                                            | 72 |  |  |

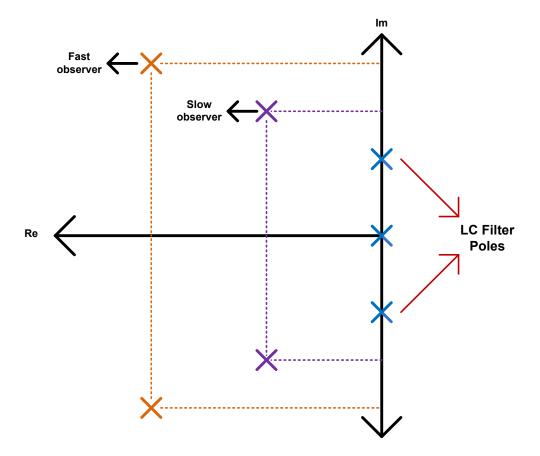

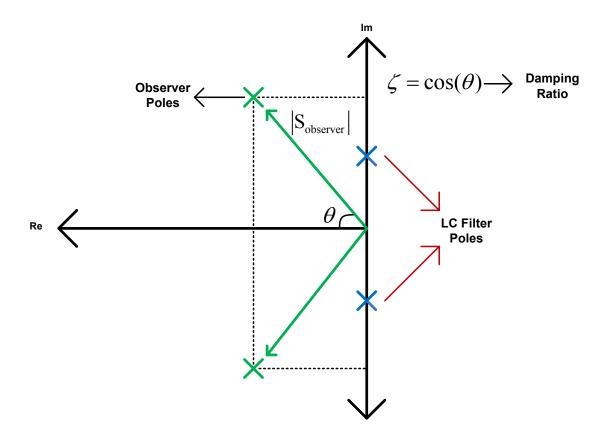

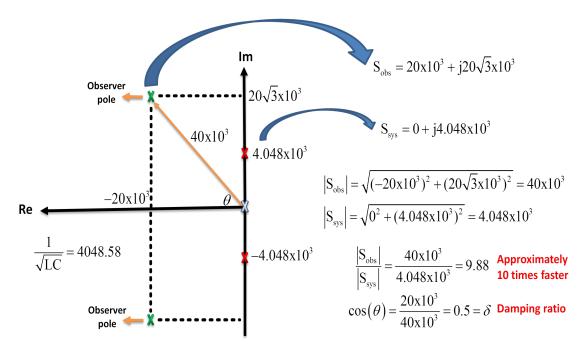

| Figure | 4.6 Poles of the system and observers                                                                                                                    | 73 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 4.7 Selection of observer poles                                                                                                                          | 74 |

| Figure | 4.8 Model predictive control scheme for nine-switch inverter                                                                                             | 75 |

| Figure | 4.9 Nine-switch inverter under unknown load conditions                                                                                                   | 76 |

| Figure | 4.10 Algorithm flow chart for predictive controller                                                                                                      | 77 |

| Figure | 4.11 Poles location of observer and LC filter for simulation                                                                                             | 79 |

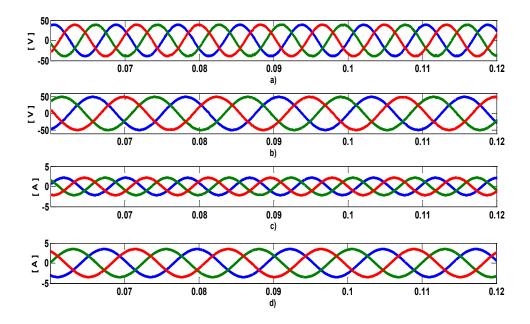

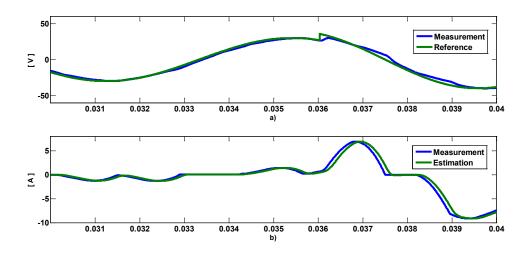

| Figure | 4.12 Simulation results a) Output upper capacitor voltage b) Output lower capacitor voltage c) Upper load current d) Lower load current                  | 80 |

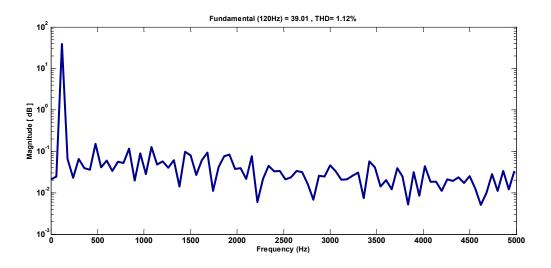

| Figure | 4.13 Output upper capacitor voltage frequency spectrum under linear load condition                                                                       | 80 |

| Figure | 4.14 Output lower capacitor voltage frequency spectrum under linear load condition                                                                       | 81 |

| Figure | 4.15 Upper load current frequency spectrum under linear load condition                                                                                   | 81 |

| Figure | 4.16 Lower load current frequency spectrum under linear load condition                                                                                   | 82 |

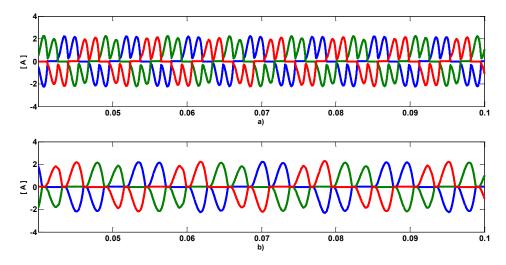

| Figure | 4.17 Output filter inductro current under linear load condition a) Upper inductor current waveform b) Lower inductor current waveform                    |    |

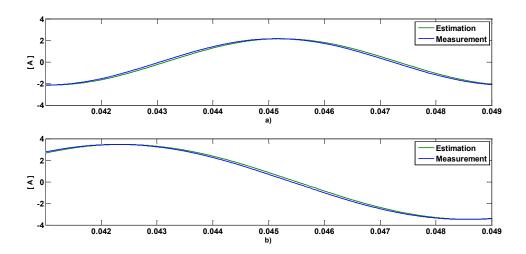

| Figure | 4.18 Load current estimation under linear load condition a) Upper load current estimation b) Lower load current estimation                               | 83 |

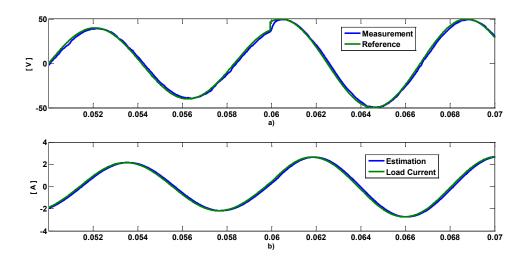

| Figure | 4.19 Dynamic response of predictive controller under linear load condition a) Upper output capacitor voltage b) Loweroutput capacitor voltage            | 83 |

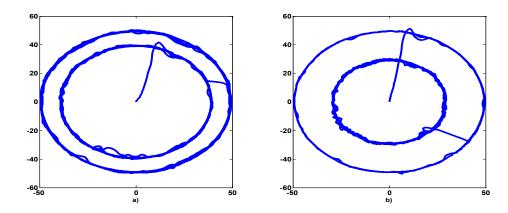

| Figure | 4.20 Phase plane plot for capacitor voltage a) Upper output capacitor voltage plot b) Lower output capacitor voltage plot                                |    |

| Figure | 4.21 Dynamic behavior of upper observer and controller under linear load conditions a) Upper output capacitor voltage b) Upper loadcurrent estimation    | 84 |

| Figure | 4.22 Dynamic behavior of lower observer and controller under linear load conditions a) Lower output capacitor voltage b) Lower load current estimation . | 85 |

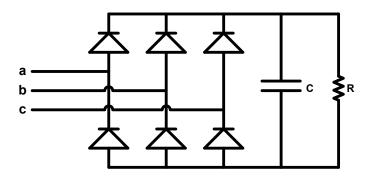

| Figure | 4.23 Diode-bridge rectifier                                                                                                                              | 85 |

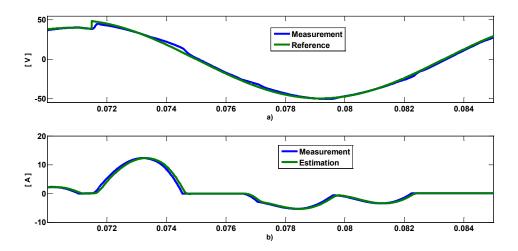

| Figure | 4.24 Output filter capacitor voltage under unbalanced load condition a) Upper capacitor voltage b) Lower capacitor voltage                               | 86 |

| Figure | 4.25 Output load current under unbalanced load condition a) Upper load current  Lower load current                                                              | b)<br>86 |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure | 4.26 Frequency spectrum of output voltage under nonlienar load condition a) Upper output voltage frequency spectrum b) Lower output voltage frequency spectrum. |          |

| Figure | 4.27 Filter inductor current under unbalanced load condition a) Upper filter current b) Lower filter current                                                    | 38       |

| Figure | 4.28 Dynamic response of predictive controller under unbalanced load condition a) Upper capacitor voltage b) Lower capacitor voltage                            |          |

| Figure | 4.29 Dynamic reponse of observer under unbalanced load condition a) Upper load current estimation b) Lower load current estimation                              |          |

| Figure | 4.30 Step response ofthe system a) Upper capacitor voltage b) Upper load current estimation                                                                     |          |

| Figure | 4.31 Step response of the system a) Lower capacitor voltage b) Lower load curre estimation                                                                      |          |

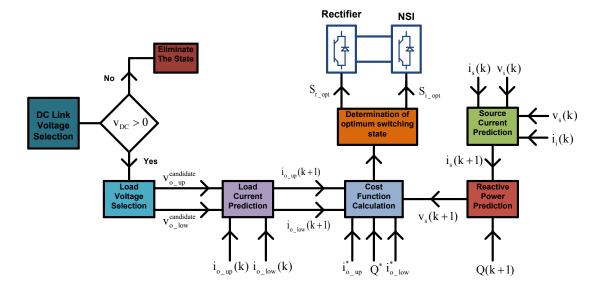

| Figure | 5.1 Predictive control scheme for dual-output indirect matrix converter                                                                                         | 96       |

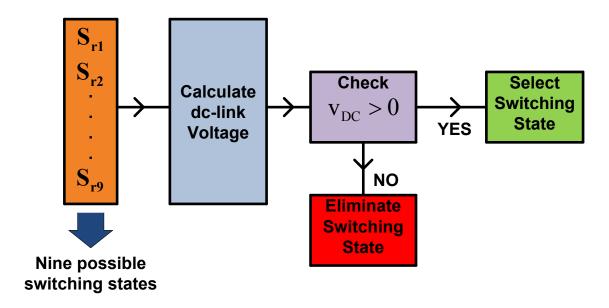

| Figure | 5.2 Switching state elimination process .                                                                                                                       | 97       |

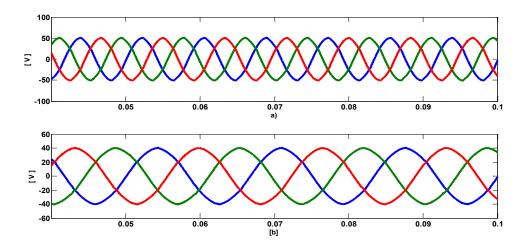

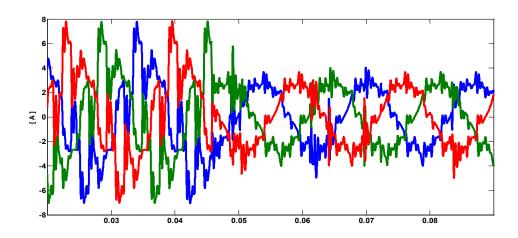

| Figure | 5.3 Simulation results for dual-output indirect matrix converter a) Supply voltage b) Upper load current c) Lower load current d) Source current                |          |

| Figure | 5.4 Frequency spectrum of upper load current.                                                                                                                   | 99       |

| Figure | 5.5 Frequency spectrum of lower load current                                                                                                                    | )(       |

| Figure | 5.6 Frequency spectrum of source current10                                                                                                                      | )C       |

| Figure | 5.7 Dynamic response of proposed control scheme a) Upper load current b) Low load current                                                                       |          |

| Figure | 5.8 Phase planeplot of output load current a) Upper load current b) Lower load current                                                                          | )1       |

| Figure | 5.9 DC-link voltage                                                                                                                                             | )2       |

| Figure | 5.10 DC-link current 10                                                                                                                                         | )2       |

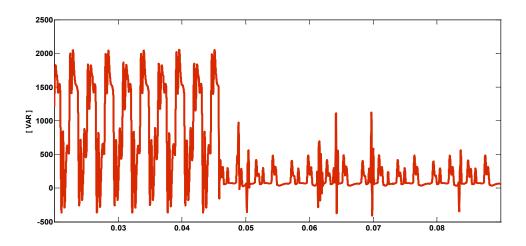

| Figure | 5.11 Instantanesous reactive power                                                                                                                              | )3       |

| Figure | 5.12 Supply current 10                                                                                                                                          | )4       |

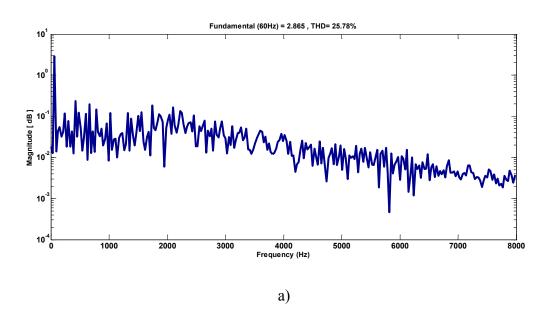

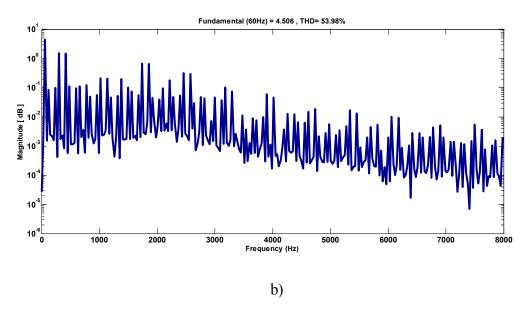

| Figure 5 | 5.13 Frequency spectrum of input current a) Spectral con | ntents with reactive power |

|----------|----------------------------------------------------------|----------------------------|

| ŀ        | b) Spectral content without reactive power control       | 105                        |

## LIST OF SYMBOLS

| α                | Coefficient of characteristic equation                 |

|------------------|--------------------------------------------------------|

| $\theta$         | Angle of the vector (radian)                           |

| Š                | Damping ratio                                          |

| $\sigma$         | Normalized current error                               |

| A                | Weighting factor                                       |

| В                | Weighting factor                                       |

| C                | Weighting factor                                       |

| $C_{\mathrm{f}}$ | Input filter capacitance                               |

| $C_1$            | Control constraint for load current control problem    |

| $C_2$            | Control constraint for reactive power control problem  |

| D                | Weighting factor                                       |

| $f_1$            | Sub-optimization problem (Load current control)        |

| $f_2$            | Sub-optimization problem (Reactive power control)      |

| $f_3$            | Sub-optimization problem (Switching frequency control) |

| g                | Cost function                                          |

| I                | Identity matrix                                        |

| $i_{DC}$         | DC-link current (A)                                    |

i<sub>f</sub> Output filter current (A)

$i_o^e$  Load current error (A)

$i_o(k)$  Load current value at instant k (A)

$i_o(k+1)$  Load current value at instant k+1 (A)

i<sub>o low</sub> Lower load current (A)

$i_{o_{up}}$  Upper load current (A)

$i_{o low}^*$  Upper load current reference (A)

$i_{o_{up}}^{*}$  Lower load current reference (A)

K Observer gain

L Load inductance (H)

L<sub>f</sub> Input filter inductance (H)

m Size of the solution set for reactive power control

n Size of the solution set for switching frequency control

P Active power (W)

p Pole of the system

Q Reactive power (VAR)

Q\* Reactive power reference (VAR)

R Load resistance  $(\Omega)$

$R_f$  Input filter resistance ( $\Omega$ )

S Switch position

S(k+1) Future switching combination

$S_{LC}$  LC filter pole

S<sub>observer</sub> Observer pole

$S_{svs}$  Pole of the system

T Instantaneous transfer matrix

T<sub>1</sub> Sub-finite solution set (Load current control)

T<sub>2</sub> Sub-finite solution set (Reactive power control)

T<sub>3</sub> Sub-finite solution set (Switching frequency control)

$T_{CSR}$  Interconnection of rectifier stage

T<sub>L</sub> Interconnection matrix of lower load

Ts Sampling period

T<sub>U</sub> Interconnection matrix of upper load

u(k) Control input

v<sub>c</sub> Output filter capacitor voltage (V)

$V_{DC}$  DC-link voltage (V)

v<sub>i</sub> Input voltage (V)

$V_{i low}$  Lower load voltage (V)

$V_{i_{up}}$  Upper load voltage (V)

v<sub>o</sub> Output voltage (V)

v<sub>s</sub> Supply voltage (V)

x State vector

x Estimated state

x(k) State variable

x(k+1) Future value of state variable

$x^*(k+1)$  Future reference of state variable

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 FINITE CONTROL SET MODEL PREDICTIVE CONTROL

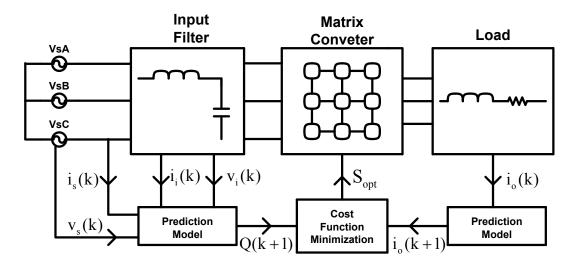

Finite Control Set Model Predictive Control (FCS-MPC) is an optimization-based control approach that minimizes a cost function to optimize system behavior. MPC offers many advantages: in particular it makes it easy to handle multiple control objectives, which can be represented by a multi-term cost function. The inclusion of nonlinearities and constraints in the control law is straightforward. The MPC techniques applied to power converters have been classified into two main categories [1]-[3]: Continuous Control Set MPC and Finite Control Set MPC. In the first category, a modulator is used to generate gate signals and the control signal is continuous [4]-[7]. In the second category, FCS-MPC solves a multi-objective optimization problem by making an exhaustive search over a finite control set and determining the optimal control action. The main advantage of FCS-MPC lies in the direct application of the control action to the converter without requiring a modulation stage.

A power converter can be modeled as a discrete system with a finite number of possible states and MPC uses this discrete model of the system to predict the future evolution of the controller variables [8]-[13]. Future values of control variables are calculated by using prediction equations for each possible switching state and these predictions are used to calculate the errors with respect to the reference values. The user-

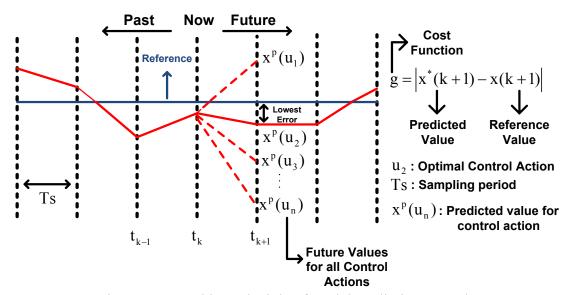

defined cost function, which is a function of these errors, is calculated for all possible switching states to determine the optimal switching combination. This optimal switching combination, which represents the optimal control action, is applied to the converter for the next time interval [14]-[18]. The user-defined cost function is usually a multiobjective cost function, so that more than one control objectives can be achieved simultaneously. Note that, in order to implement a multi-objective controller using conventional linear control technique, a multi-loop controller is typically required with all the associated complications. In MPC, different control objectives can be controlled simultaneously using a single control loop. Since MPC does not use a modulator and a change of switching state does not occur at every sampling time, the system has a variable switching frequency. Different control objectives can be introduced in the cost function, such as output load current control, reduction of the switching frequency and minimization of instantaneous reactive power [19]-[23]. The future values of the state of the system are predicted for a single predefined horizon. The working principle of MPC is shown in Figure 1.1 for the case of a single control objective and a one-time-step horizon. A variable x is required to follow a reference x\*. A time t<sub>k</sub> all possible future states are calculated by applying to the system model for all possible control variables. The control action that provides the minimum error is selected for the  $t_k$ - $t_{k+1}$  time interval.

The optimal action is determined by minimizing the cost function and the whole process is repeated again for each sampling instant considering the new measured data. All possible switching states are evaluated to determine the best-suited switching combination and the so-determined optimal switching state is selected for the next time

interval. The number of calculations required is directly related to the number of possible switching states. In case of three-phase voltage source inverter, there are eight possible switching states and calculating predictions for the eight possible switching states is a manageable task. But in case of DMC or multi-level converter, real-time implementation of the MPC algorithm may be problematic given the large number of possible switching states and consequently the large amount of calculations required.

Figure 1.1: Working principle of model predictive control

Although the theory of MPC was developed in the 1970s, its application in power electronics and drives is more recent due to the high computation burden. The fast microcontrollers available in the last decade have triggered research in new control schemes for power converter systems, such as MPC. For this application, the optimization problem is made easier by the discrete nature of power converters. Fast digital control platforms make online optimization process possible and solving online optimization problem by using the finite number of switching states is a real possibility. The design of finite control set model predictive control consists of the following steps:

- 1) Modeling of power converter with finite states

- 2) Derivation of the relationship between switching states and control variables

- 3) Design of cost function that represents the desired system behavior

- 4) Development of an algorithm that finds the switching state that minimizes the cost function

In general, these four steps can be used to design a model predictive controller.

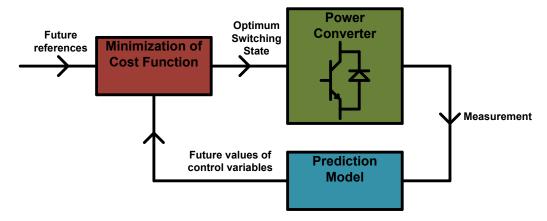

The general model predictive control scheme for power converter systems is shown in Figure 1.2.

Figure 1.2: General predictive control scheme for power converters

#### 1.2 DIRECT MATRIX CONVERTER

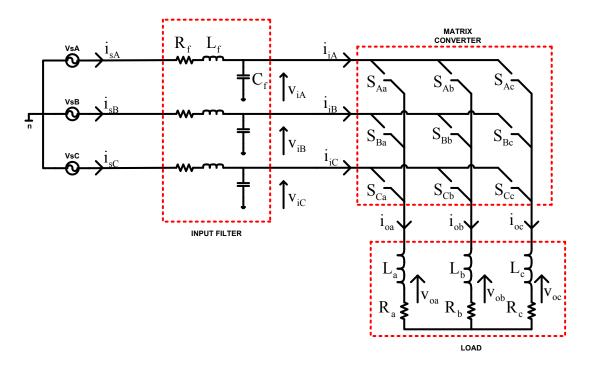

The Direct Matrix Converter (DMC) was introduced by Venturini and Alesina [24]. The Direct Matrix Converter is a good alternative to the traditional two stage ac-dc-ac topology, because it can convert an ac source to an ac load without a dc-link and without large energy storage components. This significantly improves overall system reliability by eliminating failure-prone dc-link electrolytic capacitors and may improve efficiency, given the single power conversion stage. The DMC, shown in Figure. 1.3, has

nine bi-directional switches, which directly connect the three-phase power supply to the three-phase ac load. An L-C filter is used at its input to improve the quality of the input current. At the output, it delivers voltages and currents to the load with high quality and without restrictions on frequency, which can be different from the source frequency. Moreover, the DMC is power bidirectional, i.e., it allows power to flow from source to the load and in the opposite direction, which means that it is suitable for regenerative load applications. Two switching restrictions must be considered for proper operation. Firstly, since the DMC is fed by a voltage source, any switching state that shorts two input lines is not allowed. Secondly, since the converter output is inductive, an interruption of the output current is not allowed, because it would lead to large voltage spikes. Considering these two switching restrictions, 27 possible switching combinations are allowed for proper operation.

Figure 1.3: Direct matrix converter topology

These 27 switching combinations can be considered as possible control actions for DMC. With reference to Figure 1.3, the switching function of a bi-directional switch of DMC is defined as,

$$S_{ij} = \begin{cases} 1, & \text{switch on} \\ 0, & \text{switch off} \end{cases}$$

(1.1)

The two switching restrictions described above can be represented by the conditions

$$S_{Aj} + S_{Bj} + S_{Cj} = 1 \quad \forall \quad j \in \{a, b, c\}$$

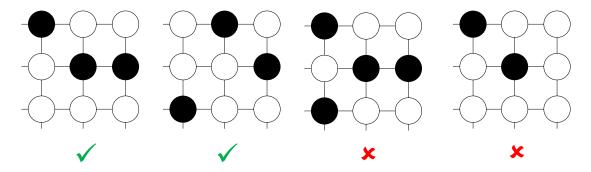

which require that each output be connected to one and only one input. Several switching combinations for DMC are shown in Figure 1.4. The first two switching combinations are allowed for proper operation, whereas the remaining two are not. In case of the third switching combination, two input lines are shorted. For the fourth combination, the output load current is interrupted.

Figure 1.4: Switching combinations for direct matrix converter

#### 1.3 DUAL OUTPUT NINE-SWITCH INVERTER

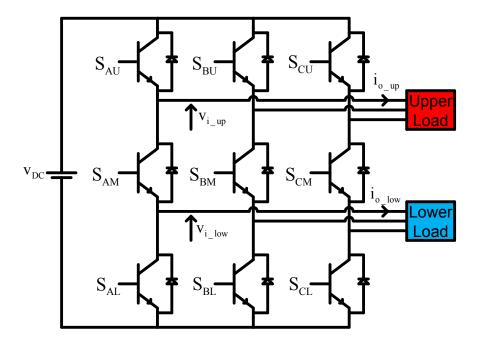

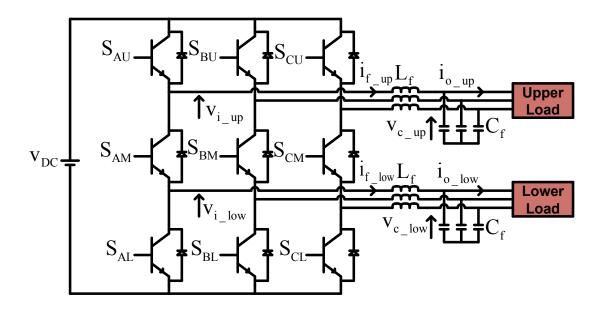

Conventional three-phase inverters have a single three-phase ac output and six switches. The Nine-Switch Inverter (NSI) is a dual-output inverter (see Figure 1.5), recently introduced [25], having only nine switches. Note that two separate inverters would require a total of 12 switches. The NSI is based on the conventional voltage-source

inverter with three series switches and it has been used for various applications such as industrial motor control and electrical vehicle motor drives [26]. For the NSI topology, each leg has three switches and there are eight different ON-OFF positions. All switches on the same leg cannot be turned on at the same time to avoid DC bus short circuit. Another switching restriction is that at least two switches on the same leg should be on, so that floating of the connected load is avoided.

Figure 1.5: Nine-switch inverter topology

Considering these switching restrictions, each leg can be in three different switch combinations which are called {1, 0, -1} [30]. Possible switch positions are illustrated in Table I with I=A, B, C identifying the inverter legs. The NSI has 27 possible switching states, but, since some of them redundant, only 15 of these switching states are sufficient to control the two ac loads. Frequencies and amplitudes of the two ac loads can be different and the two loads can be controlled independently. Benefit of using only 15

switching states instead of all 27 allowable switching states is that computational burden is decreased.

Table 1-1 Switches positions of Legs

|                            | $S_i = 1$ | $S_i = 0$ | $S_i = -1$ |

|----------------------------|-----------|-----------|------------|

| $S_{iU}$                   | ON        | OFF       | ON         |

| $\mathbf{S}_{\mathrm{iM}}$ | OFF       | ON        | ON         |

| $S_{iL}$                   | ON        | ON        | OFF        |

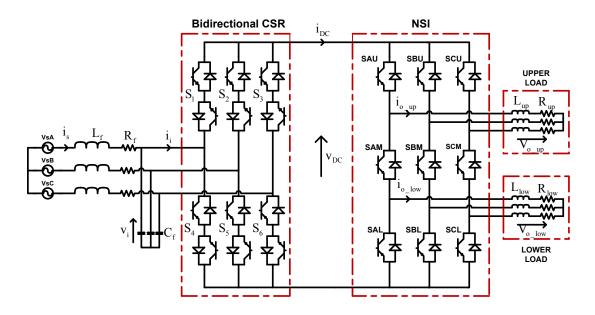

#### 1.4 Dual-Output Indirect Matrix Converter

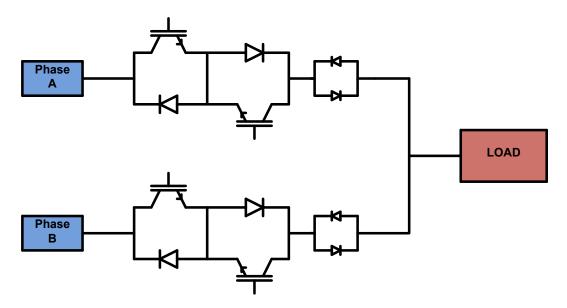

The Indirect Matrix Converter (IMC) is a two-stage ac-ac power converter that can convert ac source to ac load without a dc-link capacitor or other storage components. Dual-output indirect matrix converter is based on the traditional IMC topology but the conventional six-switch inverter is replaced by a nine-switch inverter. Many matrix converter topologies have been proposed, mostly of the single-output type [22],[28]. The dual-output IMC, shown in Figure 1.6, uses four-quadrant switches in the bidirectional Current Source Rectifier (CSR) stage and no dc-link capacitor is required. The rectifier stage is connected to the Nine-Switch Inverter stage [27].

Figure 1.6: Dual-Output Indirect Matrix Converter Topology

#### 1.5 RESEARCH OBJECTIVES

On the one hand, model predictive control method has several advantages, such as allowing easy inclusion of nonlinearities and providing fast dynamic response. On the other hand, the MPC method has several drawbacks:

- 1. Real-time implementation of MPC incurs high computational burden

- 2. There is no analytical procedure to adjust the weighting factors for multiobjective optimization problem

- A complete system model must be derived since MPC method uses this model to predict control variables

- 4. MPC implementation is not straightforward for several power converter topologies, such as dual-output power converters.

In this dissertation, these four disadvantages are considered and methods are proposed to overcome them. In general, the proposed research can be divided into four parts that will be described in later chapters.

Chapter 2 presents efficient real-time implementation of MPC for direct matrix converter. Finite Control Set MPC (FCS-MPC) imposes a very high computational burden that causes significant hardware requirements and suitable technology should be used to implement this control algorithm due to its complex computational scheme. The objective is to reduce execution time of MPC algorithm by taking advantage of the fact that MPC control is very parallelizable. A solution exploiting the parallel processing capability of FPGAs is proposed.

**Chapter 3** presents novel model predictive control method based switching state elimination. In a multi-optimization problem, adjusting weighting factors is problematic since there is no specific procedure to pick weighting factors. Switching state elimination technique is proposed to control several control objectives without weighting factors.

Chapter 4 investigates model predictive control performance under unknown load condition. The proposed method can control a nine-switch inverter and two ac loads are controlled simultaneously. Full-order observers are used to estimate load currents and the proposed method is tested under linear and nonlinear load conditions. This chapter presents the observer design procedure and predictive controller design for a nine-switch inverter.

Chapter 5 presents the model predictive control scheme for a dual-output indirect matrix converter. This chapter includes modeling of dual-output IMC and the design steps for predictive control scheme. Predictive controller design procedure covers

derivation of system model and future expression of control variables, cost function design and selecting weighting factors. The proposed method controls two ac loads and instantaneous reactive power simultaneously.

Chapter 6 gives a summary of the contributions and proposes some future work.

#### **CHAPTER 2**

# FPGA-BASED MODEL PREDICTIVE CONTROLLER FOR DIRECT MATRIX CONVERTER

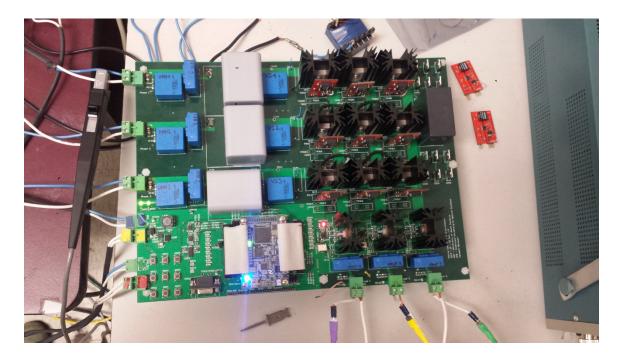

The model predictive control method implementation imposes a very high computational burden and causes significant hardware requirements for real-time implementation. Suitable technology should be used to implement this control algorithm due to its computationally intensive computation scheme. In conventional real-time implementation of model predictive control for direct matrix converter, DSP and FPGA are both used to ensure fast processing operation and preserve performance of the predictive controller [41]-[43]. In this work, a fully FPGA-based real-time implementation of model predictive control is proposed for DMC, eliminating the need for a DSP. This simplifies system implementation. A 1.6 kW DMC prototype was built to validate the proposed method. An Altera-DEO nano FPGA evaluation board is used to implement the control algorithm.

#### 2.1 DIRECT MATRIX CONVERTER MODEL

The MPC uses the discrete-time model of the system for predicting the future behavior of the controlled variables and calculates a cost function related to multiple control objectives to find its minimum. For this reason, derivation of the system model is critical in the model predictive control approach. With reference to Figure 1.3, the instantaneous transfer matrix T is defined as

$$\mathbf{T} = \begin{bmatrix} \mathbf{S}_{Aa} & \mathbf{S}_{Ab} & \mathbf{S}_{Ac} \\ \mathbf{S}_{Ba} & \mathbf{S}_{Bb} & \mathbf{S}_{Bc} \\ \mathbf{S}_{Ca} & \mathbf{S}_{Cb} & \mathbf{S}_{Cc} \end{bmatrix}$$

(2.1)

The elements of matrix **T** are 1 when the corresponding switch is closed and zero when it is open. The load and input voltages can be expressed as vectors. The output load voltage is defined as

$$\mathbf{v}_{\mathbf{o}} = \begin{bmatrix} \mathbf{v}_{oa} & \mathbf{v}_{ob} & \mathbf{v}_{oc} \end{bmatrix}^{\mathsf{T}} \tag{2.2}$$

and the input voltage vector is defined as

$$\mathbf{v}_{i} = \begin{bmatrix} \mathbf{v}_{iA} & \mathbf{v}_{iB} & \mathbf{v}_{iC} \end{bmatrix}^{T} \tag{2.3}$$

Thus the relationship between input and output voltages is given by

$$\mathbf{v}_{\mathbf{o}} = \mathbf{T}^{\mathsf{T}} \mathbf{v}_{\mathbf{i}} \tag{2.4}$$

The input and output load current vectors are defined as

$$\mathbf{i}_{i} = \begin{bmatrix} i_{iA} & i_{iB} & i_{iC} \end{bmatrix}^{T} \tag{2.5}$$

$$\mathbf{i}_{o} = \begin{bmatrix} i_{oa} & i_{ob} & i_{oc} \end{bmatrix}^{\mathrm{T}} \tag{2.6}$$

The relationship between input and output load current is given by

$$\mathbf{i}_{i} = \mathbf{T}\mathbf{i}_{0} \tag{2.7}$$

In this work, an RL circuit is used as the load model and therefore the continuous model of RL load is

$$\mathbf{v}_{o} = \mathbf{R}\mathbf{i}_{o} + \mathbf{L}\frac{\mathbf{d}\mathbf{i}_{o}}{\mathbf{d}t} \tag{2.8}$$

where R is the load resistance and L is the load inductance. The dynamic model of the second order input filter can be expressed as

$$\mathbf{v}_{s} = L_{f} \frac{d\mathbf{i}_{s}}{dt} + R_{f} \mathbf{i}_{s} + \mathbf{v}_{i}$$

(2.9)

$$\mathbf{i}_{s} = \mathbf{i}_{i} + C_{f} \frac{d\mathbf{v}_{i}}{dt} \tag{2.10}$$

#### 2.2 Model Predictive Control for Direct Matrix Converter

The predictive control strategy is based on the idea that only a finite number of possible switching states can be generated by power converters. For the selection of the appropriate switching state to be applied, a proper cost function needs to be defined and this cost function will be evaluated for each possible switching state. Prediction of the future values of control variables is used to calculate the cost function and the switching state that minimizes the cost function is selected. There are three steps to design the predictive controller:

- 1) Building the prediction model of the system

- 2) Defining control objectives

- 3) Designing cost function

A discrete-time model is used to predict future value of the control variables and the cost function defines the desired system behavior.

#### 2.2.1 Prediction Model

In order to obtain the discrete-time model, the forward Euler approximation is used

$$\frac{di_o}{dt} \approx \frac{i_o(k+1) - i_o(k)}{Ts}$$

(2.11)

The load current prediction equation can be obtained using (2.8) and (2.11). The future load current is given in (2.12). In (2.12),  $v_o(k)$  is the candidate voltage vector and  $i_o(k)$  is the load current measurement.

$$i_o(k+1) = \frac{Ts}{L} v_o(k) + i_o(k) (1 - \frac{RTs}{L})$$

(2.12)

The second order input filter can be represented by a state-space model.

$$\begin{bmatrix} \mathbf{v}_{i} \\ \mathbf{v}_{i} \\ \vdots \\ \mathbf{i}_{s} \end{bmatrix} = \mathbf{A}_{c} \begin{bmatrix} \mathbf{v}_{i} \\ \mathbf{i}_{s} \end{bmatrix} + \mathbf{B}_{c} \begin{bmatrix} \mathbf{v}_{s} \\ \mathbf{i}_{i} \end{bmatrix}$$

(2.13)

where

$$A_{c} = \begin{bmatrix} 0 & \frac{1}{C_{f}} \\ \frac{-1}{L_{f}} & \frac{-R_{f}}{L_{f}} \end{bmatrix} \quad \text{and} \quad B_{c} = \begin{bmatrix} 0 & \frac{-1}{C_{f}} \\ \frac{1}{L_{f}} & 0 \end{bmatrix}$$

(2.14)

The discrete time state-space model of the input filter can be expressed as follows

$$\begin{bmatrix} v_{i}(k+1) \\ i_{s}(k+1) \end{bmatrix} = \Phi \begin{bmatrix} v_{i}(k) \\ i_{s}(k) \end{bmatrix} + \Gamma \begin{bmatrix} v_{s}(k) \\ i_{i}(k) \end{bmatrix}$$

(2.15)

where

$$\Phi = e^{A_c Ts}$$

and  $\Gamma = \int_0^{Ts} e^{Ac(Ts-\tau)} B_c d\tau$  (2.16)

The future source current can be determined by using a discrete-time model of the input filter. Source current prediction is defined as

$$i_{s}(k+1) = \Phi(2,2)i_{s}(k) + \Phi(2,1)v_{i}(k) + \Gamma(2,1)v_{s}(k) + \Gamma(2,2)i_{i}(k)$$

(2.17)

Instantaneous input active and reactive power can be predicted using source current prediction and source voltage measurement. Input active and reactive power are expressed in  $\alpha$ - $\beta$  frame and the Park transformation is used to calculate real and imaginary components of associated vectors. Subscript  $\alpha$  and  $\beta$  represent real and imaginary components of source current and source voltage. Reactive power is calculated as the imaginary part of the product of the source voltage multiplied by the complex conjugate of the source current.

$$Q(k+1) = Im \left\{ \mathbf{v}_{s}(k+1) \, \overline{\mathbf{i}_{s}(k+1)} \right\} = \mathbf{v}_{s\beta}(k+1) \mathbf{i}_{s\alpha}(k+1) - \mathbf{v}_{s\alpha}(k+1) \mathbf{i}_{s\beta}(k+1)$$

(2.18)

Instantaneous input active power is defined as

$$P(k+1) = \text{Re}\left\{\mathbf{v}_{s}(k+1)\,\overline{\mathbf{i}_{s}(k+1)}\right\} = \mathbf{v}_{s\alpha}(k+1)\mathbf{i}_{s\alpha}(k+1) + \mathbf{v}_{s\beta}(k+1)\mathbf{i}_{s\beta}(k+1)$$

(2.19)

#### 2.2.2 Cost Function Design

Cost function design is critical in model predictive control approach because it defines switching state selection criteria. The most commonly used terms in a cost function are the ones that represent a variable following a reference. These terms can be expressed as an error between future value of the control variable and its reference:

$$g = |x^*(k+1) - x(k+1)|$$

(2.20)

where  $x^*(k+1)$  is the reference value and x(k+1) is the predicted value. The cost function term g is the absolute value of the error between predicted value and its reference. In this work, there are three control objectives: output load current control, minimization of instantaneous reactive power and reduction of switching frequency (to

reduce switching losses and improve efficiency). The output load current control can be achieved by minimizing the absolute error between future load current and future load current reference. The load current control term can be expressed in orthogonal coordinates

$$g_{1} = \left| i_{o\alpha}^{*}(k+1) - i_{o\alpha}(k+1) \right| + \left| i_{o\beta}^{*}(k+1) - i_{o\beta}(k+1) \right|$$

(2.21)

where  $i_{o\alpha}(k+1)$  and  $i_{o\beta}(k+1)$  are the real and imaginary parts of the predicted load current. This prediction is obtained using the load model, which is defined in (2.12).  $i_{o\alpha}^*(k+1)$  and  $i_{o\beta}^*(k+1)$  are the real and imaginary part of the future load current reference. For simplicity, it can be assumed that the reference load current does not change significantly in one sampling period in case of short sampling period. In this case, the  $i_o^*(k+1) \approx i_o^*(k)$  approximation can be used to predict the future load current. On the other hand, extrapolation methods can be used to predict sinusoidal reference in case of a large sampling period. Lagrange extrapolation method can be used to predict the load current reference [58]. Lagrange extrapolation technique is given in (2.22).

$$i_o^*(k+1) = \sum_{h=0}^{n} (-1)^{n-1} \begin{bmatrix} n+1 \\ h \end{bmatrix} i_o^*(k+h-n)$$

(2.22)

Sinusoidal load current reference can be predicted in case of n=2.

$$i_{o}^{*}(k+1) = 3i_{o}^{*}(k) - 3i_{o}^{*}(k-1) + i_{o}^{*}(k-2)$$

(2.23)

The objective of controlling instantaneous reactive power can be easily achieved by introducing term g2, which penalizes the absolute error of reactive power.

$$g_2 = |Q^*(k+1) - Q(k+1)|$$

(2.24)

The reactive power is predicted using the input filter model and the reference value for reactive power control,  $Q^*(k+1)$ , can be chosen as zero. In power electronics applications, obtaining unity input power factor is really important to improve power quality. Classical modulation methods to obtain unity input power factor are complicated, whereas the predictive control approach is very simple. Power factor can be improved significantly by introducing reactive power minimization term in the cost function.

Another important control objective is to reduce the average switching frequency of the system. For power converter systems, switching losses are typically proportional to the switching frequency, so reducing the switching frequency of the system is highly desirable to reduce losses and improve efficiency. Since FCS-MPC does not use modulator and a change of switching state does not necessarily occur at every sampling time, the system has a variable switching frequency. To assign a cost to the average switching frequency, one can count the number of switches that commutate when a new switching state is applied to the system. The cost for controlling switching frequency is defined as

$$g_3 = |S(k+1) - S(k)|$$

(2.25)

where S(k) is current switching combination and S(k+1) is future switching state. The difference between future and current switching states is penalized to reduce switching frequency. The total cost function of the system, including terms (2.21), (2.24) and (2.25), is expressed in (2.26).

$$g = Ag_1 + Bg_2 + Cg_3 (2.26)$$

A, B and C are the weighting factors. Typically they are adjusted empirically. These weighting factors need to be properly tuned to obtain desired system performance.

Otherwise, the controller performance is affected significantly. In this work, the weighting factor for output load current control term A, is chosen as 1 and an offline-tuning technique is used to adjust weighting factor B and C.

### 2.2.3 MODEL PREDICTIVE CONTROL SCHEME

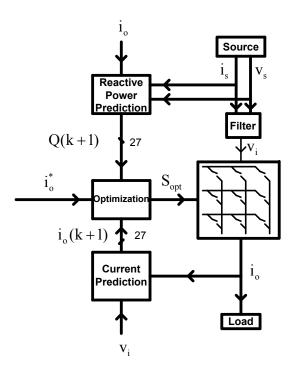

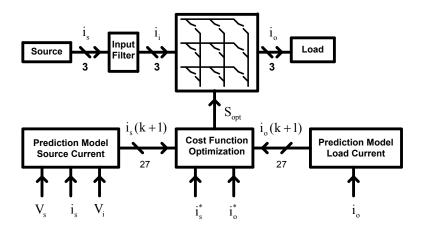

The predictive control scheme for the direct matrix converter is represented in Figure 2.1. The MPC selects the switching state of the converter that minimizes the cost function, defined in (2.26). The load model is used to predict the future load current and the input filter model is used to predicted instantaneous reactive power. Consequently, the valid switching state that produces the lowest value of the cost function is selected for the next sampling period.

Figure 2.1: Model predictive control scheme for direct matrix converter

Predictive control approach can effectively control the output current and instantaneous reactive power. The strategy presented allows the input power factor to be regulated by simple and straightforward means. This method can be easily implemented by taking advantage of the present technologies, which will be explained in a later chapter, and

implementation of MPC algorithm is much simpler compared to conventional control technique.

#### 2.3 Issues with Conventional Real-Time Implementation

In conventional real-time implementation of model predictive control for matrix converter, Digital Signal Processors (DSPs) and Field-Programmable Gate Arrays (FPGAs) are both used to complete all control calculations and several other tasks, such as commutation and protection. In the literature, using both DSP and FPGA is the preferred technology for implementing the MPC algorithm for matrix converter but it requires two separate digital control platforms for proper operation [48]-[50]. The main issue with the conventional real-time implementation approach is that DSP devices can do only serial computing and they are not fast enough to complete all required tasks in case of a short sampling period. For this reason, a separate digital control platform, such as FPGA, is used to complete other tasks such as safe commutation scheme and protection, and DSP is only responsible for performing control calculations. When control schemes based on model predictive control method are implemented experimentally, a large number of calculations are required. For the power converters, if DSP is used for performing model predictive control calculations, there will be a delay in control actuation [51]. In order to overcome this problem, several delay compensation methods have been reported [55],[56]. The main drawback of the delay compensation technique is that an accurate system model is required. Otherwise delay compensation techniques do not work well. For all these reasons, decreasing the time required for control calculations is highly desirable. The conventional real-time implementation is shown in Figure 2.2.

Conventional real-time implementation is complicated because interfacing between two digital control platform is not straightforward in terms of software architecture. The interface between FPGA and DSP also contributes a delay because a finite time is required to transfer the data from DSP to FPGA for generating the appropriate gate signals. As a result, the interfacing between to digital control platform and the delay in applying new control actions is problematic in conventional method.

Figure 2.2: Conventional real-time implementation for direct matrix converter

#### 2.4 Proposed Real-Time Implementation Method

Field Programmable Gate Arrays (FPGAs) are a better solution for the real-time implementation of FCS-MPC method over traditional microcontrollers and DSPs, since the discrete nature of predictive controller fits well with the features of FPGA devices, such as parallel processing capability and pipelining. Parallel computational capability of FPGA devices can be used to perform independent control calculations during the same clock cycle, so that the time required for MPC implementation can be significantly

reduced [59]. This overcomes the control delay issue and provides better performance under transient conditions, especially in the presence of in accuracies in the prediction model.

Figure 2.3: Comparison between conventional method and proposed method

FCS-MPC is a strategy to control selected state variables by performing a real-time optimization. At the beginning of the current time intervals, measurements of the current values of the state variables are performed. The trajectories of the state variables in the following time interval are calculated for all possible states using the system model and the optimal switching state is selected by evaluating the possible values of a cost function. The state resulting in the minimal cost is selected. The so-determined optimal switching state is applied at the beginning of the following time interval. The one-step-ahead prediction for control goals must be completed within the current time interval. The computational time can be dramatically reduced by parallel computing implementation of the FCS-MPC, as shown in Figure 2.4. Since future control variables values for different switching states are independent, these calculations can be

parallelized. Notice, however, that some blocks depend on the output of other blocks, and therefore proper order of execution is essential. For example, current cost calculations require the predicted current results. The order of execution is controlled by a synchronizer block which is based on Finite State Machine (FSM).

Figure 2.4: Parallel implementation of model predictive control

Figure 2.5: Finite state machine for current cost calculation

The current prediction is enabled when the measurements for the current step are available at the inputs. When each block finishes its task, a done signal is generated and sent to the control block. After completion of the current prediction calculations, the cost calculation blocks are enabled. When these complete, the total cost calculation starts and when this is completed the optimization process starts. Figure 2.6 shows the FPGA architecture for the predictive controller. Notice how the synchronizer block sends enable and done signals to each block to ensure proper order of execution.

Figure 2.6: FPGA architecture for predictive controller

The model predictive controller is implemented using an Altera DEO-Nano board. The prediction and optimization steps present the largest computational burden and there is a tradeoff between calculation time and required FPGA resources, such as memory bits and logic elements. The number of memory bits and logic elements required

is directly related to the number of parallel computation blocks. To improve execution speed, the calculations are performed in parallel, but this increases demand for resources. When the sampling period is greater than the time required for control calculations, the FPGA resources can be shared between functional blocks in order to minimize the area used to implement the model predictive control method. In Figure 2.4, each current prediction sub-block calculates the future value of the output load current based on the same measurement data for different switching combination. In this way, the computation delay is decreased considerably, but larger area of the FPGA is used. For this reason, the area-time optimization needs to be considered in the controller design. In Figure 2.7, different computation architectures are shown and highest speed can be achieved when the control calculations are fully paralleled.

Figure 2.7: Time-Area optimization

#### 2.5 HARDWARE PLATFORMS AND EXPERIMENTAL RESULTS

Many different subsystems have to be built and interconnected to realize a matrix converter evaluation board. The two-phase input single-phase output prototype is used to test all sub-circuits and software. Direct matrix converter topology has a complicated

commutation scheme, four-step commutation technique, and output load current direction needs to be sensed to implement the four step commutation method. Over current and voltage protections are tested using this prototype and VHDL code for interfacing between analog-to-digital (ADC) chip and FPGA board was developed. Basic schematics for the two-phase input single-phase output prototype is shown in Figure 2.8 and the hardware prototype is shown in Figure 2.9.

Figure 2.8: Two-phase input single-phase output topology

Figure 2.9: Two-phase input single-phase output topology

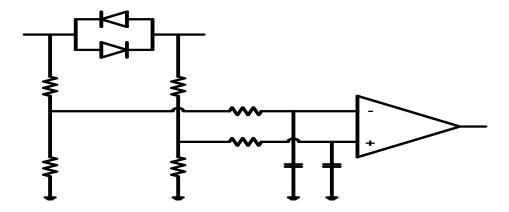

The matrix converter topology requires four-quadrant switches, which do not have free-wheeling diodes. For this reason, a proper commutation scheme must be implemented to prevent short circuits between input phases and interruption of the inductive load current [46], [54]. The current flowing through the switches must be actively controlled and several commutation methods for proper commutation have been reported [45]. The most common technique for commutation is the four-step commutation technique, typically implemented in FPGA using a finite state machine. It is important to accurately measure the current direction to implement the four-step commutation technique. Different ways to detect the current direction are possible for proper DMC operation [47]. For detection of output load current direction, two Schottky diodes are connected in anti-parallel in

each output phase. The voltage-drop (maximum 380 mV in amplitude) on top of the output voltage is sensed using an instrumentation amplifier, given the large DC offset. The output signal coming from the instrumentation amplifier is galvanically isolated using a high-speed gate-logic optocoupler. This signal can be directly read by the FPGA. Figure 2.10 shows the circuit used for load current sign detection using the instrumentation amplifier. Figure 2.11 shows that current direction measurement and zero crossing of the output load current is precisely detected.

Figure 2.10: Output load current measurement circuit

a)

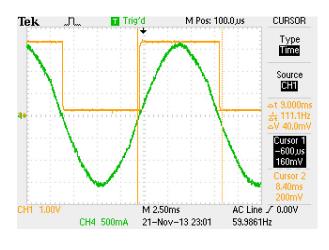

Figure 2.11: a) Load current direction detection b) Rising edge c) Falling edge

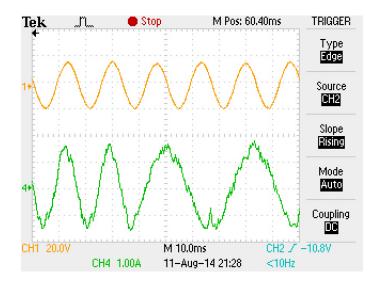

The delay between each subsequent step is set at TD=1.5  $\mu$ s. This value is chosen based on turn-on/off characteristic of the power semiconductor devices. Gate waveforms generated from FPGA-based implementation are shown in Figure 2.12 in case of positive load current and in Figure 2.12b in case of negative load current.

Figure 2.12: Four-step commutation a) Positive load current b) Negative load current

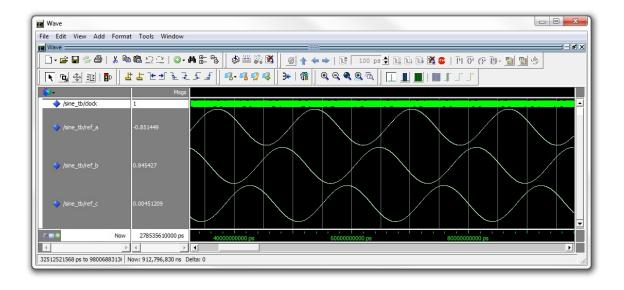

The source current and output load current are sensed using the LAH 25-NP current sensor from LEM. The source voltage, input filter capacitor voltage and output load voltage are sensed using LV 25-P from LEM. Since the FPGA board, Altera DEO-Nano, used to implement the control algorithm, does not have Analog-to-Digital Converter (ADC), an external ADC circuit, ADC128S102 from Texas Instruments, is used for the analog-to-digital conversion process. The external ADC chip has 8 channels and 12 bit resolution. Communication between FPGA and the external ADC chip is implemented over SPI protocol. For sinusoidal reference, the use of extrapolation methods for the reference can compensate the delay in the reference tracking. In this work, a ROM block from Altera FPGA is used to generate a look-up-table with necessary values for the sine wave. The future value of the reference current can be directly read from look-up-table. RTL for reference generation is shown in Figure 2.13 and simulation results for reference generation block is presented in Figure 2.14. ModelSim Altera is used to simulate the testbench code.

Figure 2.13: Register Transfer Level (RTL) for reference generation

Figure 2.14: Reference generation using ROM block

To verify the performance of the parallel implementation method, a 1.6 kW direct matrix converter prototype was built. The IGBTs used are IKW40N120T2 from Infineon Technologies. A serial UART connection is added to the prototype to communicate with a host PC and a clamp circuit is used for protection. The experimental setup is shown in Figure 2.15. Currents and voltages are measured using Tektronix TDS 2014B

oscilloscope and LeCroy DA1855A differential amplifier is used to measure output load voltage. The three-phase input voltage is at 60 Hz.

Figure 2.15: Direct matrix converter prototype

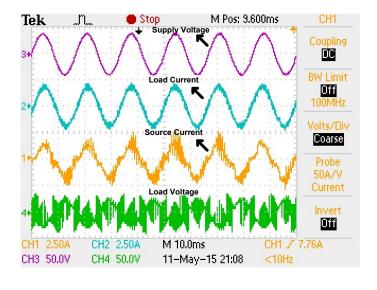

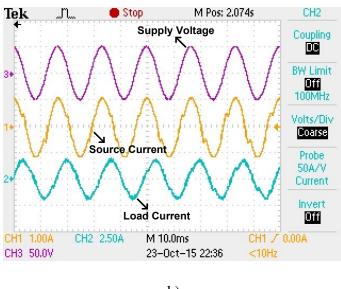

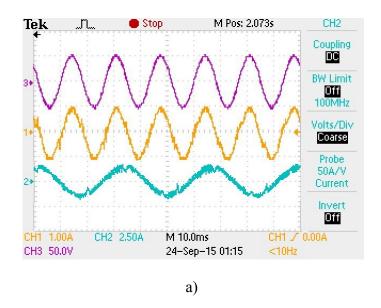

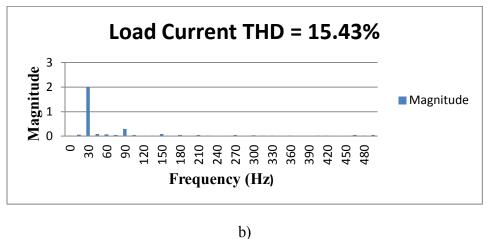

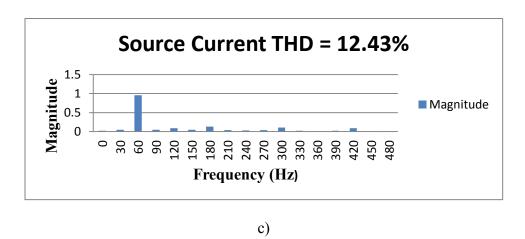

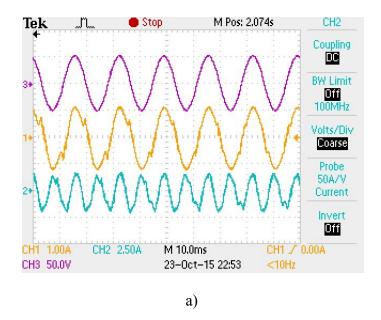

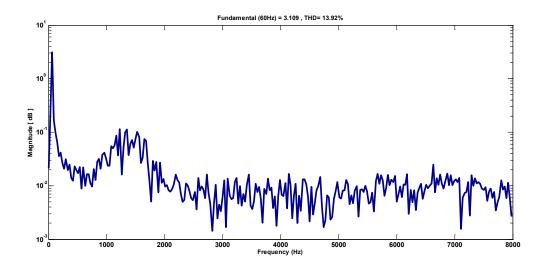

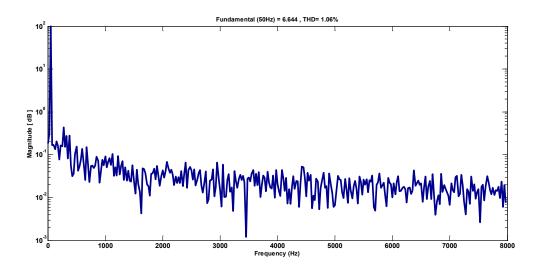

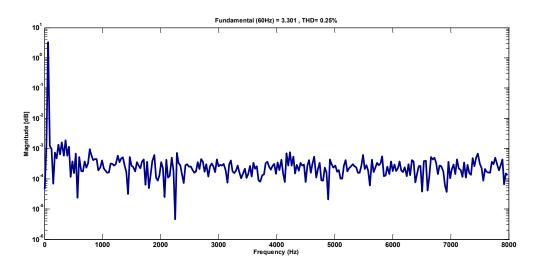

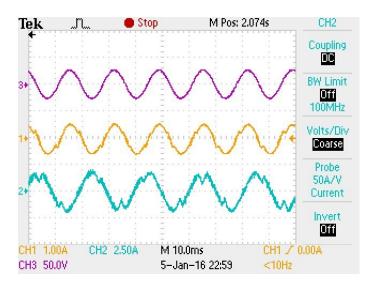

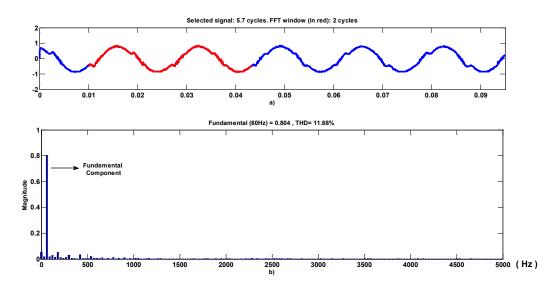

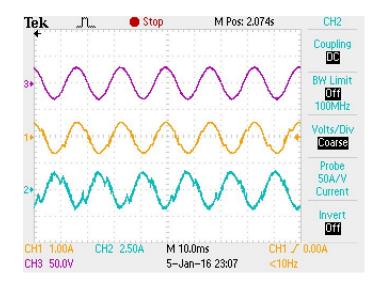

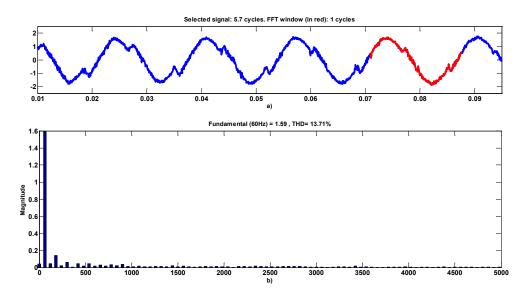

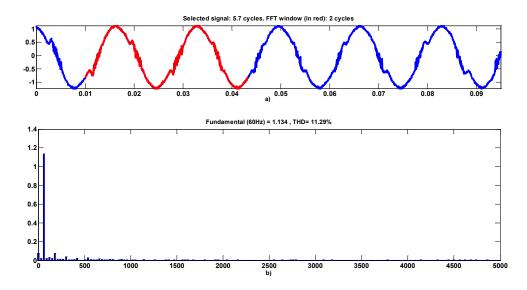

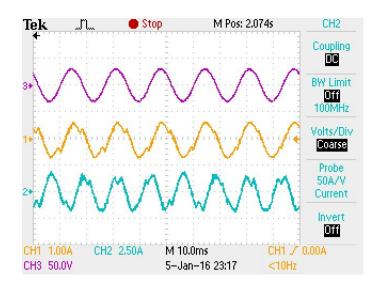

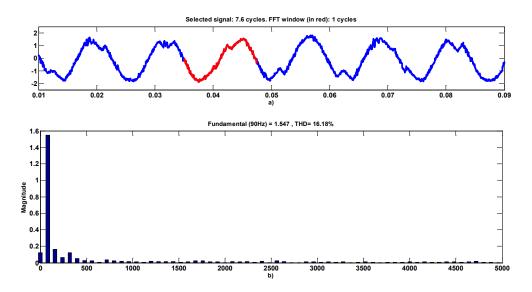

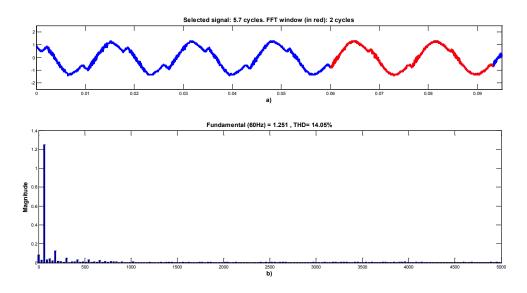

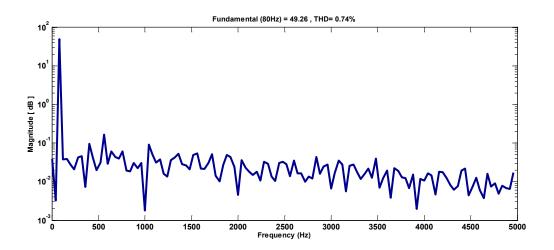

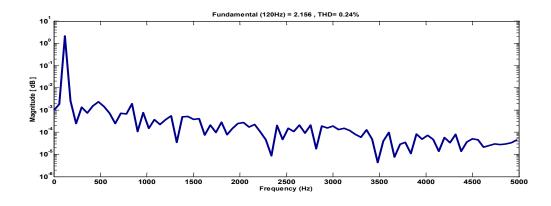

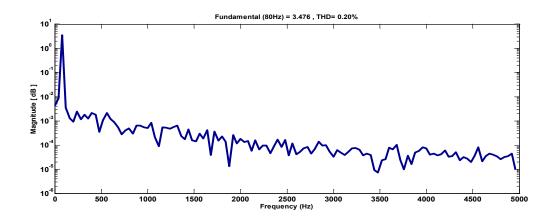

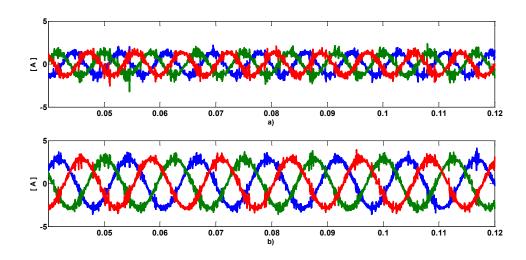

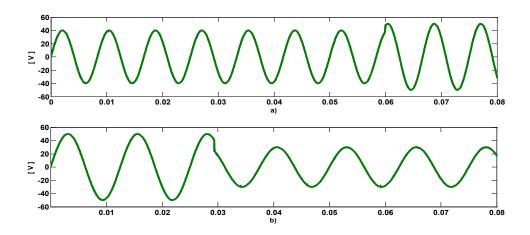

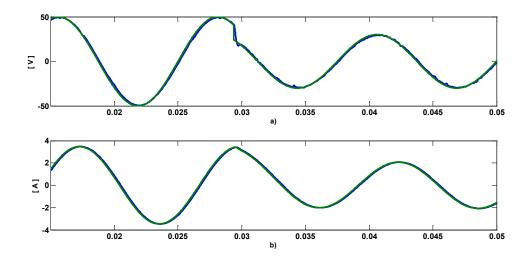

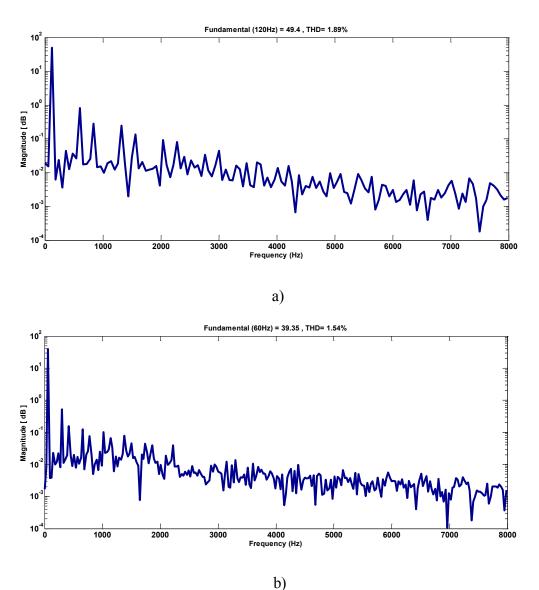

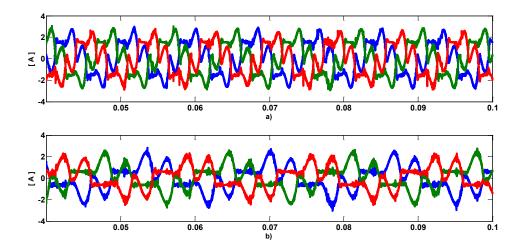

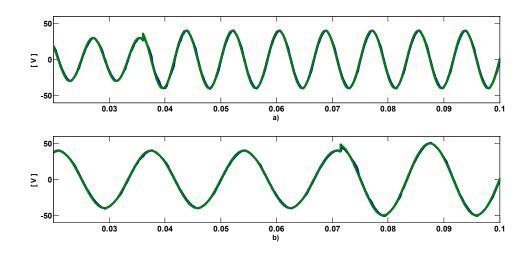

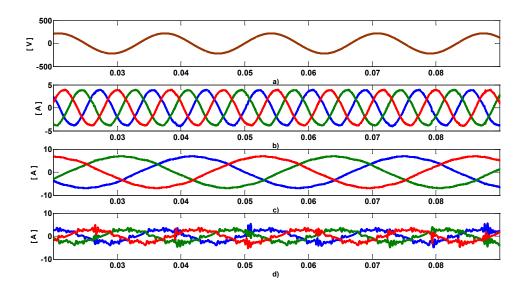

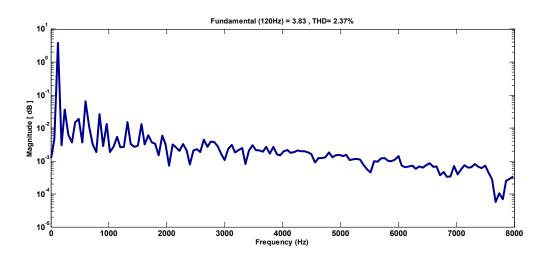

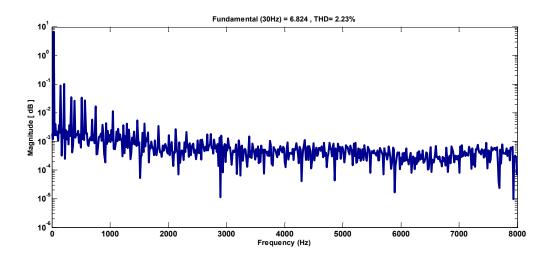

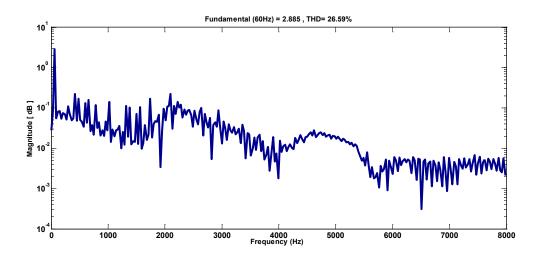

Figure 2.16 shows experimental results without reactive power control, B=0, AND with reactive power control, B=0.042. Load voltage waveform is the voltage across both the load resistor and load inductor and consequently it is a chopped waveform at the switching frequency. Figure 2.16 shows that source current is less distorted for the case of non-zero B. The sampling time is 16 μs. Output load current THD is 8.67% and source current THD is 12.43% in case of 30 Hz load current reference, see Figure 2.17.b and c. Figure 2.18 shows that load current THD is 15.14% and source current THD 18.33% in case of 120 Hz load current frequency. The effect of weighting factors is important in model predictive control method. Load current THD, source current THD and average switching frequency are tabulated in Table 2.1. Effects of the weighting factors are investigated for the case of load current frequency equal to 30 Hz.

a)

b)

Figure 2.16: Experimental results in case of 60 Hz reference a) Experimental waveforms without reactive power control b) Experimental waveforms with reactive power control

The results show that increasing values of B and C improve the corresponding control objectives at the cost of increased load current THD. However, good compromise values can be found, as shown by the experimental results.

Figure 2.17: Experimental results in case of 30 Hz reference a) Experimental waveforms b) Load current frequency spectrum c) Source current frequency spectrum

Load Current THD = 15.14%

2.5

2

1.5

0

0 60 120 180 240 300 360 420 480 540 600 660 720 780

Frequency (Hz)

b)

Source Current THD = 18.33%

1.5

0 60 120 180 240 300 360 420 480 540 600 660 720 780

Frequency (Hz)

Figure 2.18: Experimental results in case of 120 Hz reference a) Experimental waveforms b) Load current frequency spectrum c) Source current frequency spectrum

In the cost function equation (2.26), weighting factor A is 1. THD values and average switching frequency are listed for different values for B and C.

Table 2.1: Effect of weighting factors

| A | В      | С     | Load Current | Source Current | Average   |

|---|--------|-------|--------------|----------------|-----------|

|   |        |       | THD          | THD            | Frequency |

| 1 | 0      | 0     | 6.32%        | 48.12%         | 13.12 kHz |

| 1 | 0.0012 | 0.002 | 8.13%        | 21.57%         | 11.23 kHz |

| 1 | 0.0068 | 0.002 | 8.50%        | 11.93%         | 12.79 kHz |

| 1 | 0.0068 | 0.047 | 8.67%        | 12.43%         | 10.48 kHz |

| 1 | 0.015  | 0.047 | 10.16%       | 12.68%         | 11.12 kHz |

| 1 | 0.030  | 0.06  | 12.77%       | 12.65%         | 9.2 kHz   |

| 1 | 0.12   | 0.06  | 19.14%       | 28.78%         | 9.65 kHz  |

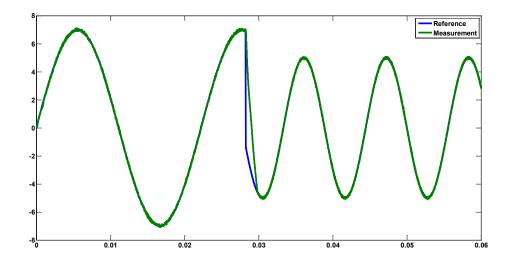

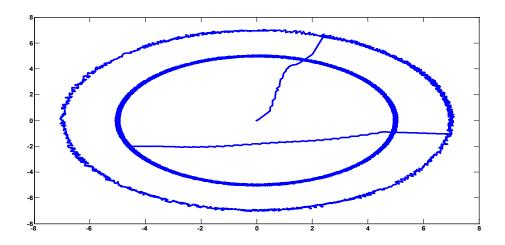

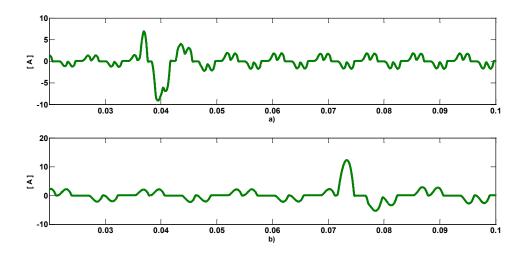

In order to evaluate the dynamic performance of the predictive control method, the frequency of the load current is changed in a step-wise fashion from 60 Hz to 30 Hz and the resulting step response is shown in Figure 2.19. According to experimental results, predictive control technique works well under both steady-state and transient conditions. Reference tracking is quite good and FPGA-based implementation provide good dynamic response.

Figure 2.19: Dynamic response of FPGA-based model predictive controller

#### 2.6 DISCUSSION AND CONCLUSION

This chapter presented FPGA-based model predictive control method for direct matrix converter. The proposed real-time implementation technique eliminates the need for DSP, reduces complexity of hardware implementation and shortens computation time by exploiting parallelization in the FPGA. Control algorithm and tasks are performed in the FPGA and the advantages of implementing digital controllers using FPGA are demonstrated. In the predictive control method, increasing the number of control objectives increases the computation burden significantly. In FPGA-based implementation, execution time can be kept almost the same even if more control objectives need to be controlled. FPGA resources and execution time are tabulated in Table 2.2 in case of different numbers of control objectives.

Table 2.2: FPGA resources and execution time vs number of control objectives

|                       | Combinational    | Dedicated      | Memory Bits   | <b>Execution Time</b> |

|-----------------------|------------------|----------------|---------------|-----------------------|

|                       | <b>Functions</b> | Logic Register |               |                       |

| One Objective         | 3875/22320       | 1617/22320     | 110592/608256 | 1.72 μs               |

| - Load current        | (17 %)           | (7 %)          | (18%)         |                       |

| Two Objective         | 4390/22320       | 1691/22320     | 110592/608256 | 1.89 µs               |

| - Load current        | (20 %)           | (8 %)          | (18%)         |                       |

| - Switching Frequency |                  |                |               |                       |

| Two Objective         | 21787/22320      | 5500/22320     | 120317/608256 | 2.12 μs               |

| - Load current        | (98 %)           | (25 %)         | (19%)         |                       |

| - Switching Frequency |                  |                |               |                       |

| - Reactive Power      |                  |                |               |                       |

It can be concluded that, if control calculations are fully paralleled using an FPGA, significant extra execution time is not required in the case of multiple objectives, but only a small amount of extra time is required since source current and source voltage need to be calculated for future reactive power calculation. As shown in Table 2.2, execution time does not change significantly as long as FPGA resources are used to parallelize calculations. To better understand the benefit of using FPGA devices, comparison between different digital control platforms is shown in Table 2.3.

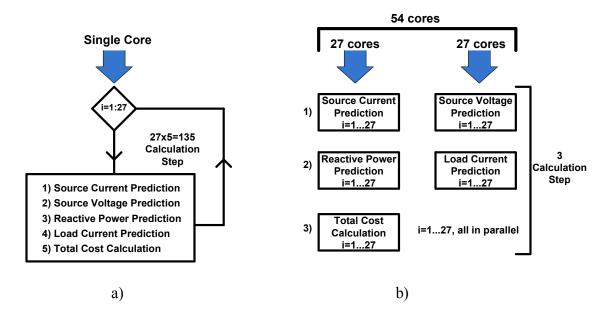

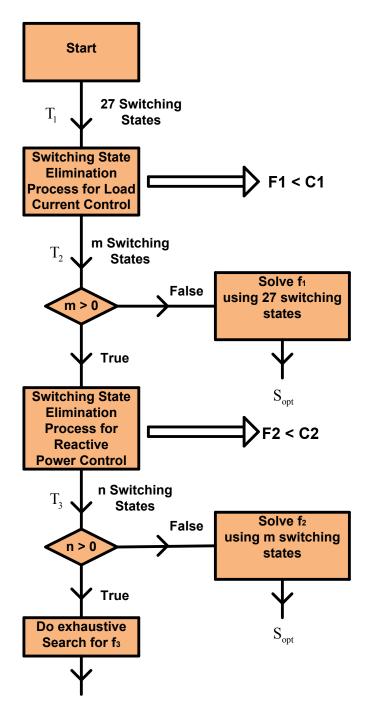

If a serial-computing device is used for MPC implementation, 135 calculation steps are required, but, on the other hand, only 3 calculation steps are required for FPGA implementation in case of fully paralleling, see Figure 2.20. In order to achieve the same execution speed with a serial-computing device, at least 45 times higher clock speed is required compared to the clock speed of FPGA used in this work (50 MHz), which corresponds to 2250 MHz. Digital control platforms having this capability are more expensive compared to a 50 MHz FPGA device. For this reason, using FPGA is the lowest-cost solution to reduce the execution time.

Figure 2.20: Calculation loop comparison a) MPC implementation by using serial-computing device b)MPC implementation by fully paralleling technique

According to Table 2.3, using multi-core DPSs with high clock speed can be a solution to reduce execution time but it is not cost effective. The other important aspect is that fixed-point devices, such as FPGAs, work faster than floating-point devices, such as DSPs, because of flexibility in the number of bits used for representing the numbers in calculations. Working with fixed-point numbers in FPGAs is not straightforward

compared to floating-point numbers. On the other hand, fixed-point implementation of algorithms yields considerable improvement in computation time at the cost of reduced accuracy of the variables and increased programming effort. The development of fixed-point software requires proper scaling of variables to prevent overflows while maintaining the accuracy. Fewer bits can be used to represent numbers in calculations resulting in high execution speed. This also leads to a reduction in accuracy and resolution. However, model predictive control approach has a discrete solution set, which means that the control signal is not continuous, so accuracy is less critical.

Table 2.3: Digital control platforms comparison

| Digital<br>Controller | Controller<br>Type | Arithmetic     | Clock<br>Speed | Calculation<br>Step | Performance<br>(Clock Speed*Core)/ |

|-----------------------|--------------------|----------------|----------------|---------------------|------------------------------------|

|                       |                    |                |                |                     | 1 clock cycle                      |

| TMS320F2812           | DSP-Single         | Fixed-Point    | 150 MHz        | 135                 | 150 MMACS                          |

|                       | Core               |                |                |                     |                                    |

| TMS320F2837           | MCU-               | Floating-Point | 200 MHz        | 68                  | 400 MMACS                          |

|                       | Dual Core          |                |                |                     |                                    |

| TMS320C6678           | DSP- 8             | Fixed-Point    | 1 GHz          | 17                  | 8192 MMACS                         |

|                       | Core               |                |                |                     |                                    |

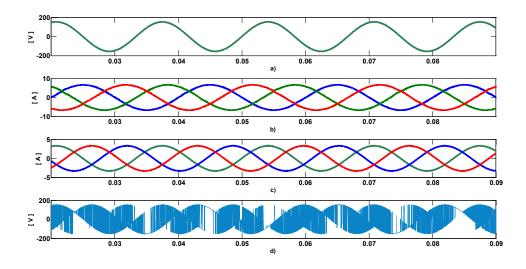

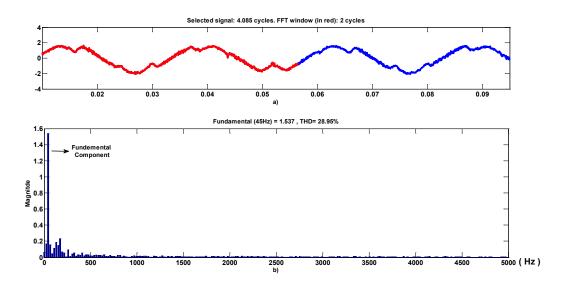

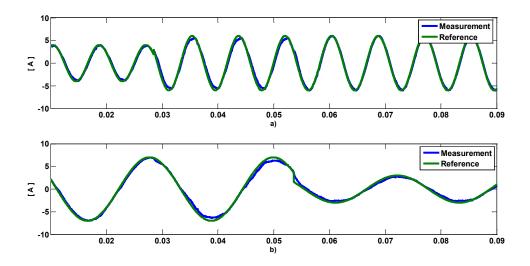

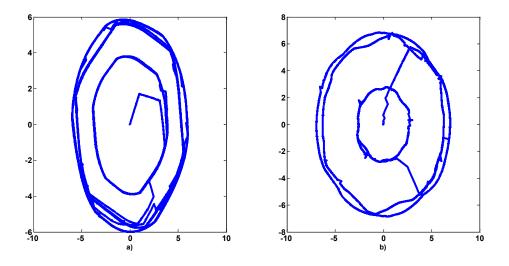

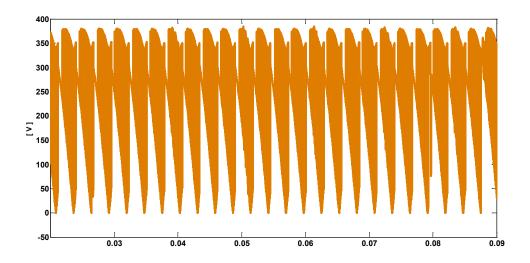

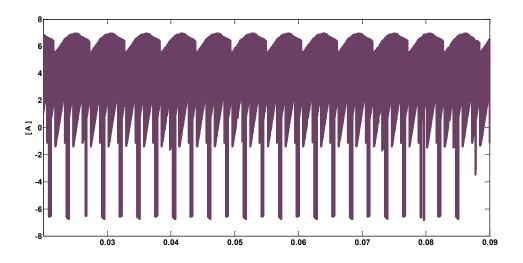

| dSPACE                | R&D                | Floating-Point | 230 MHz        | 135                 | 230 MMACS                          |